### UNIVERSITY OF PADOVA

### DEPARTMENT OF INFORMATION ENGINEERING

PH.D. SCHOOL IN INFORMATION ENGINEERING INFORMATION SCIENCE AND TECHNOLOGY XXXI CLASS

## High Performances Systems for Applications of Quantum Information

*Ph.D. Candidate:* Andrea STANCO

Supervisor: Ch.mo Prof. Paolo VILLORESI

Course coordinator: Ch.mo Prof. Andrea NEVIANI "It would be possible to describe everything scientifically, but it would make no sense; it would be without meaning, as if you described a Beethoven symphony as a variation of wave pressure."

Albert Einstein

### Abstract

This thesis work is about the realization of hardware and software systems for Quantum Random Number Generation (QRNG) and Quantum Key Distribution (QKD). Such systems were developed to guarantee a full functionality for a broader investigation of these two cutting edge applications of Quantum Information field. The thesis describes in details both the hardware and the software that were developed for FPGA-CPU board, Time-to-Digital converter (TDC) devices and computers, along with QRNG and QKD specific applications and their results.

*Randy* was the first FPGA-based QRNG device to be developed; it uses a light source attenuated to single-photon level and one single-photon avalanche diode (SPAD). From the sampling of the SPAD electrical signal, the device produces random numbers through dedicated generation protocols and through the Peres unbiasing algorithm in order to maximize the output generation bit rate. Furthermore, the device allows to generate real time random numbers. This feature is used for the time setting of electro-optical components for extending Wheeler's delayed-choice experiment to space.

The same techniques were applied to a second device, *LinoSPAD*; it combines an FPGA-chip and a CMOS-SPADs array. Moreover, in this device, a TDC improves the photon detection time accuracy. Along with a dedicated post-processing based on Zhou-Bruk algorithm, the TDC allowed to reach a final bit rate equivalent to 300 Mbit/s.

As far as QKD systems are concerned, within the collaboration among the University of Padova, the Italian Space Agency (ASI) with the Matera Laser Ranging Observatory (MLRO) and the Chinese Academy of Sciences (CAS) a TDC device management software was developed. The project aim is to realize a quantum cryptographic key exchange between the Chinese satellite Micius and MLRO. The software was designed to manage the entire data acquisition synchronized with UTC time. Furthermore, another software was designed to deal with electro-optomechanical and electro-optical components. The software is aim at the time-variant compensation of the beam angular changes through the optical path.

Once again, within a collaboration between ASI and University of Padova, a full free space QKD system over tenths of kilometers was developed. It required the design of various components. This work describes the QKD source along with the dedicated FPGA board design. Such board generates the electrical impulses to control the qubit laser along with the electro-optic phase and intensity modulators.

### Sommario

Il presente lavoro di tesi tratta la realizzazione di sistemi hardware e software per Quantum Random Number Generation (QRNG) e Quantum Key Distribution (QKD). Tali sistemi sono stati sviluppati al fine di garantire una completa funzionalità per l'investigazione a tutto campo di queste due applicazioni che ad oggi risultano essere le più promettenti nell'ambito della Quantum Information. Vengono presentati in dettaglio sia l'hardware sia i software utilizzati che sono stati sviluppati per schede FPGA-CPU, dispositivi di Time-to-Digital converter (TDC) e computer. Vengono inoltre descritte le applicazioni specifiche di QRNG e QKD assieme ai risultati ottenuti.

*Randy* è stato il primo dispositivo QRNG sviluppato su scheda FPGA e utilizza una sorgente luminosa attenuata a singolo fotone e un single-photon avalanche diode (SPAD). A partire dal campionamento del segnale elettrico dello SPAD, il dispositivo produce numeri randomici tramite protocolli di generazione appositi e tramite l'applicazione dell'algoritmo di unbiasing di Peres per massimizzare il bit rate. Il dispositivo permette inoltre di generare numeri randomici in tempo reale. Questa caratteristica viene utilizzata per la gestione temporizzata di componenti elettro-ottici per l'estensione allo spazio dell'esperimento a scelta ritardata di Wheeler's.

Le stesse tecniche sono state in seguito applicate ad un secondo dispositivo, *LinoSPAD*, che integra un chip FPGA e un array di CMOS-SPAD. Tale dispositivo prevede inoltre un TDC per aumentare la precisione temporale di dectection dei fotoni. Questa caratteristica, unita all'uso di una procedure di post-processing appositamente sviluppata e basata sull'algoritmo di Zhou-Bruk, ha permesso di raggiungere un bit rate finale pari a 300 Mbit/s.

Per quanto riguarda i sistemi QKD, all'interno di un progetto di collaborazione tra l'Università di Padova, l'Agenzia Spaziale Italiana (ASI) insieme al Matera Laser Ranging Observatory (MLRO) e la Chinese Academy of Sciences (CAS) è stato sviluppato un software di gestione di un dispositivo TDC. Il progetto prevede la realizzazione di uno scambio di chiave crittografica quantistica tra il satellite cinese Micius e l'osservatorio di Matera. Il software è stato progettato per la gestione dell'intera acquisizione dati sincronizzata al tempo UTC. Inoltre è stato sviluppato anche un software per la gestione di componenti elettro-optomeccanici e elettro-ottici atti alla compensazione tempo variante delle variazioni angolari del fascio nel percorso ottico.

Sempre all'interno di una collaborazione tra ASI e Università di Padova, è stato

vi

sviluppato un sistema completo di QKD free space per distanze nell'ordine di decine di chilometri. Lo sviluppo del sistema ha richiesto la progettazione di molteplici componenti. In questo lavoro viene descritta la parte della sorgente QKD e quindi della progettazione della scheda FPGA dedicata. Tale scheda ha il compito di generare gli impulsi elettrici per il controllo del laser per la produzione dei qubit e per il controllo dei modulatori di fase e di intensità elettro-ottici.

### Ringraziamenti

Prima dell'inizio della descrizione del lavoro di tesi desidero fare alcuni dovuti ringraziamenti.

Il primo ringraziamento va al mio supervisore, il professor Paolo Villoresi. Anni fa, quando decisi di svolgere la mia tesi di laurea magistrale presso il suo gruppo di ricerca, non immaginavo cosa tale scelta avrebbe comportato. Gli anni passati al Luxor prima come tesista, poi come assegnista e infine come dottorando sono stati degli anni di incredibile scoperta e crescita sotto ogni aspetto.

Il secondo ringraziamento va al dottor Giuseppe Vallone, in arte Pino, che con la sua incredibile intuitività e immediatezza ha sempre rappresentato un saldo punto di riferimento a cui affidarsi.

In terzo luogo vorrei ringraziare i due post-doc che mi hanno fatto da mentori durante il percorso. Davide Giacomo Marangon è stato un collega prezioso, oltre che un amico, con cui ho condiviso momenti di lavoro e di discussione che mi hanno letteralmente aperto gli occhi e sono stati uno stimolo importante per la realizzazione della mia ricerca di dottorato. Daniele Dequal mi ha invece insegnato che le cose si possono realizzare senza doversi perdere in inutili paranoie.

Mi sembra doveroso ringraziare anche tutto il resto della ciurma del Luxor che è stata la mia casa per tutti questi anni. Ringraziarvi uno per uno mi è veramente impossibile ma vi porto tutti nel cuore, chi più chi meno (Costa tu sei tra i meno, ovviamente).

Infine desidero ringraziare tutta la mia famiglia per il sostegno che mi ha sempre dimostrato e per l'immancabile affetto. Ringrazio mio padre e mia madre per avermi fatto conoscere il mondo della ricerca (senza la loro storia non so se avrei mai fatto il dottorato) e mio fratello e mia sorella perchè sì.

In ultimo il ringraziamento più importante va a mia moglie Elena che ogni giorno mi ricorda che la risata è il motore che fa muovere l'essere umano e perché senza di lei le mie giornate sarebbero grigie.

## Contents

| A  | bstrac | t                                                      | iii  |

|----|--------|--------------------------------------------------------|------|

| Sc | omma   | rio                                                    | v    |

| Ri | ngraz  | iamenti                                                | vii  |

| In | trodu  | ction                                                  | 1    |

| Ι  | Har    | dware and software designs                             | 5    |

| 1  | SoC    | system and related tools                               | 7    |

|    | 1.1    | Introduction to FPGA and SoC                           | . 7  |

|    | 1.2    | ZedBoard development board                             | . 8  |

|    |        | 1.2.1 Zynq-7000 chip                                   |      |

|    | 1.3    | Vivado Design Suite                                    | . 12 |

|    | 1.4    | Xilinx SDK                                             |      |

|    | 1.5    | AXI Protocol                                           | . 12 |

|    | 1.6    | Finite State Machine                                   | . 12 |

|    |        | 1.6.1 Mealy and Moore state machine                    | . 13 |

|    |        | 1.6.2 Coding styles                                    | . 13 |

|    |        | 1.6.3 State encoding                                   | . 13 |

| 2  | FPG    | A-based system design                                  | 15   |

|    | 2.1    | Basic system schematic                                 | . 15 |

|    |        | 2.1.1 Hardware layer                                   | . 15 |

|    |        | Compiling strategies and results                       | . 17 |

|    |        | 2.1.2 Board software layer                             | . 17 |

|    |        | 2.1.3 PC software layer                                | . 18 |

|    | 2.2    | Memory management on board                             | . 19 |

|    | 2.3    | TCP connection                                         | . 20 |

|    |        | 2.3.1 Instructions communication                       | . 20 |

|    |        | 2.3.2 Data transfer                                    | . 20 |

| 3  | TD     | system design: Quntroller software for quTools devices | 23   |

|    | 3.1    | quTAU device by quTools                                | . 23 |

|    | 3.2    | Introduction to Quntroller software                    | . 24 |

|    | 3.3 | Software structure                            |    |

|----|-----|-----------------------------------------------|----|

|    |     | 0                                             |    |

|    |     | 3.3.2 QuTools Device                          |    |

|    |     | 3.3.3 GUI                                     |    |

|    |     | 3.3.4 File example                            |    |

|    |     | 3.3.5 Overall performances                    | 29 |

| II | Qu  | aantum Random Number Generation systems       | 31 |

| 4  | Qua | antum Random Number Generation                | 33 |

|    | 4.1 | Introduction                                  | 33 |

|    | 4.2 | Generation protocols and unbiasing algorithms | 34 |

|    |     | 4.2.1 Stipčević generation protocol           | 34 |

|    |     | 4.2.2 Fürst generation protocol               | 35 |

|    |     | 4.2.3 John von Neumann algorithm              | 36 |

|    |     | 4.2.4 Peres algorithm                         | 37 |

|    |     | 4.2.5 Zhou-Bruk algorithm                     | 38 |

| 5  | Ran | ndy Quantum Random Number Generator           | 41 |

|    | 5.1 | Novel approach                                | 41 |

|    | 5.2 | System overview                               | 44 |

|    |     | 5.2.1 Two SPADs for improved entropy          | 47 |

|    | 5.3 | FPGA design                                   | 47 |

|    |     | 5.3.1 Time domains                            | 47 |

|    |     | 5.3.2 Async-to-Sync                           | 50 |

|    |     | 5.3.3 Events Counter                          | 50 |

|    |     | 5.3.4 Tag Creator                             | 50 |

|    |     | 5.3.5 Tags Manager and Bit Ben                | 51 |

|    |     | 5.3.6 Random Number Generator                 | 51 |

|    |     | 5.3.7 Purificaxor                             | 51 |

|    |     | 5.3.8 Reset Handler                           | 52 |

|    |     | 5.3.9 BRAM memories                           | 52 |

|    |     | 5.3.10 Interrupts                             | 53 |

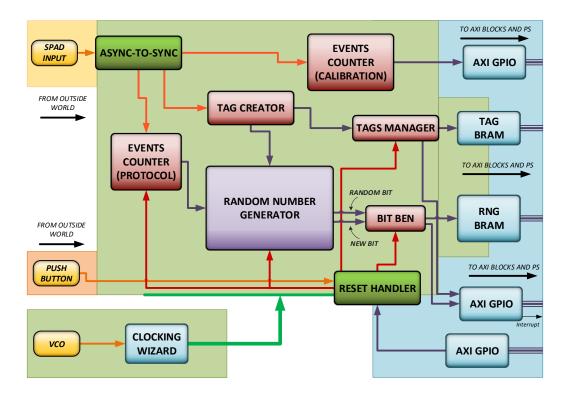

|    | 5.4 | Area, power and timing                        | 53 |

|    | 5.5 | Softwares                                     | 54 |

|    |     | 5.5.1 ZYNQ CPU software                       | 55 |

|    |     | 5.5.2 RandyApp                                | 55 |

| 6  | Rea | l time QRNG for quantum mechanics experiment  | 57 |

|    | 6.1 | Wheeler's delayed-choice experiment           | 57 |

|    | 6.2 | Experiment setup                              | 57 |

|    | 6.3 | Adapting Randy to the experiment              |    |

|    |     | 6.3.1 Synchronizing the QRNG                  |    |

|                |                  | 6.3.2 FPGA design                                           | 61  |

|----------------|------------------|-------------------------------------------------------------|-----|

| 7              | Lind             | SPAD Quantum Random Number Generator                        | 65  |

|                | 7.1              | Introduction to LinoSPAD: CMOS-SPADs array                  | 65  |

|                | 7.2              | COARSE resolution                                           | 67  |

|                | 7.3              | FINE resolution                                             | 68  |

|                | 7.4              | About FPGA-based TDC                                        | 70  |

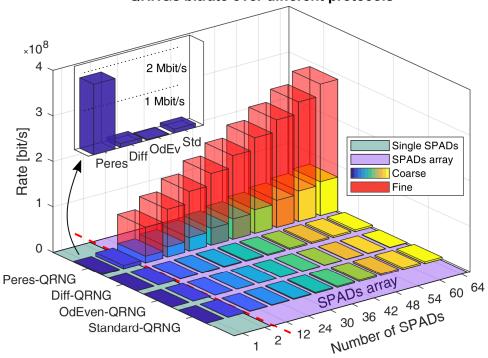

|                | 7.5              | Rates summary                                               | 73  |

| III            | [ <b>Q</b>       | uantum Key Distribution systems                             | 75  |

| 8              | Cry              | ptography and Quantum Key Distribution                      | 77  |

|                | 8.1              | Introduction and brief history of cryptography              | 77  |

|                | 8.2              | Quantum key distribution                                    | 79  |

|                |                  | 8.2.1 BB84 and other QKD protocols                          | 80  |

|                |                  | BB84 variations                                             | 81  |

|                |                  | More on QKD                                                 | 82  |

|                |                  | 8.2.2 Satellite quantum communication                       | 83  |

| 9              | Sate             | llite-to-ground QKD                                         | 85  |

|                | 9.1              | MICIUS Satellite                                            | 85  |

|                | 9.2              | Matera Laser Ranging Observatory                            | 86  |

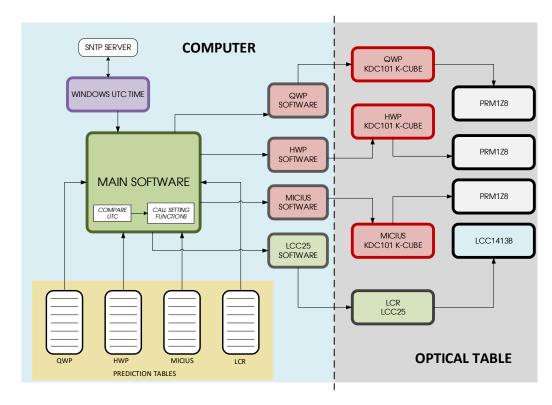

|                | 9.3              | Angle compensation and Thorlabs device controller software  | 86  |

|                |                  | 9.3.1 Thorlabs motorized rotation stage and controller      | 89  |

|                |                  | 9.3.2 Thorlabs liquid crystal retarder                      | 89  |

|                | 9.4              | GPS receiver                                                | 93  |

|                | 9.5              | PPS and quTAU synchronization                               | 94  |

|                | 9.6              | Results                                                     | 96  |

| 10             | Gro              | und-to-ground free-space QKD                                | 99  |

|                | 10.1             | Overview of the setup                                       | 99  |

|                |                  | 10.1.1 Transmitter setup                                    | 100 |

|                | 10.2             | Shortening the electrical pulse                             | 100 |

|                |                  | 10.2.1 Fixing the phase relation                            | 103 |

|                |                  | 10.2.2 External Routing and amplification                   | 103 |

|                | 10.3             | Signal for electro-optical modulators                       | 104 |

| Conclusion 107 |                  |                                                             | 107 |

| A              | Dist             | ortion and linearity on quTAU device: a behavioral analysis | 109 |

| В              | Basi             | c elements of quantum information and quantum mechanics     | 113 |

| Bi             | Bibliography 117 |                                                             |     |

# **List of Figures**

| 1.1 | ZedBoard                                                   | 9  |

|-----|------------------------------------------------------------|----|

| 1.2 | ZedBoard Block Diagram                                     | 11 |

| 2.1 | System layers scheme                                       | 16 |

| 2.2 | ZedBoard hardware scheme                                   | 18 |

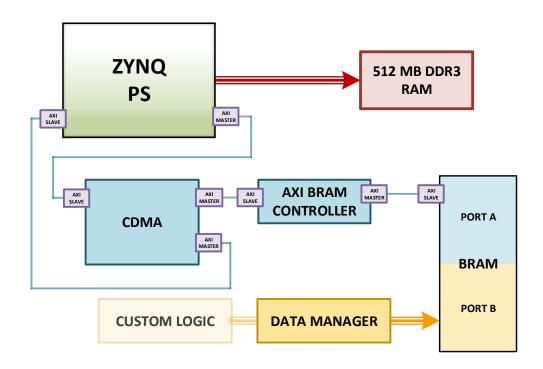

| 2.3 | ZedBoard memory scheme                                     | 19 |

| 3.1 | quTAU device                                               | 23 |

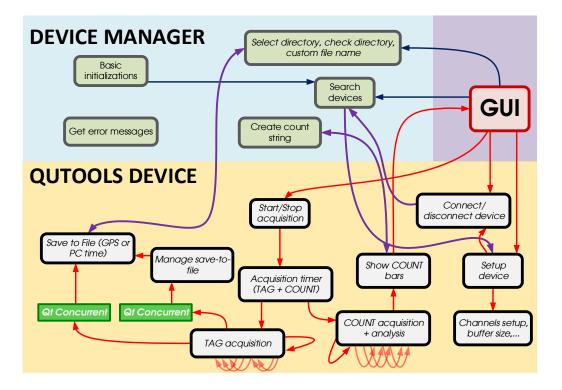

| 3.2 | Quntroller software schematic                              |    |

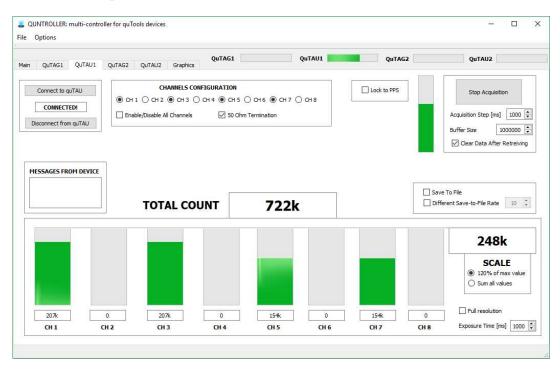

| 3.3 | View of Quntroller main window                             |    |

| 3.4 | File example of a Quntroller acquisition                   |    |

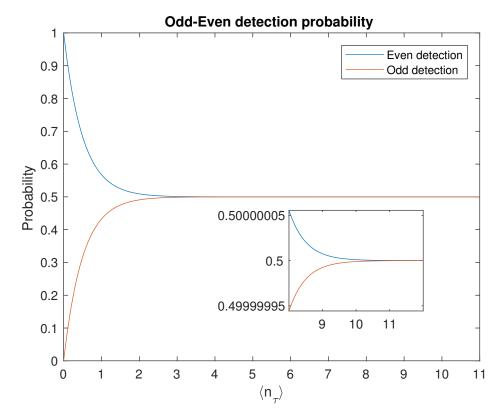

| 4.1 | OddEven detection probability.                             | 36 |

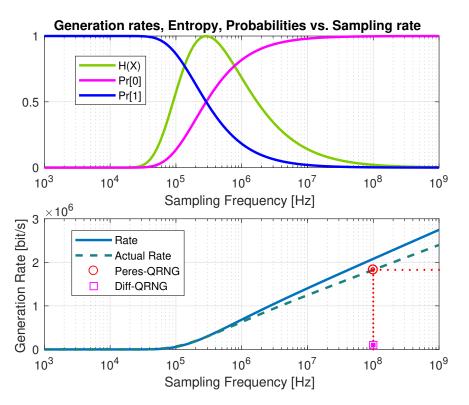

| 5.1 | Peres extraction rate and entropy                          | 43 |

| 5.2 | Schematic view of Randy                                    | 44 |

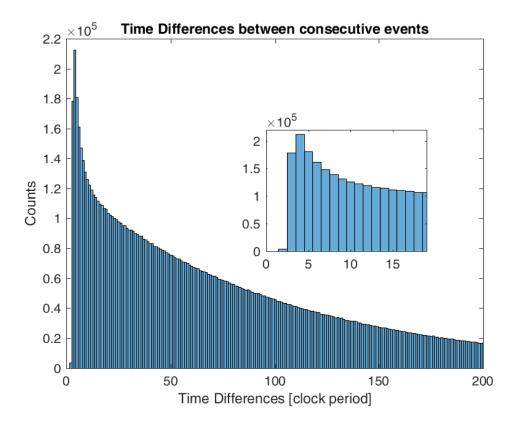

| 5.3 | Pre-processing time difference histogram                   | 45 |

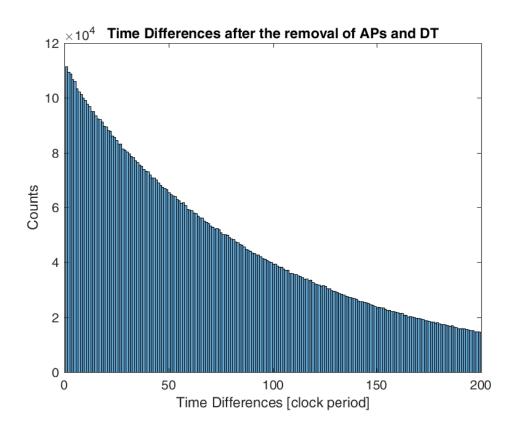

| 5.4 | Post-processing time difference histogram                  | 45 |

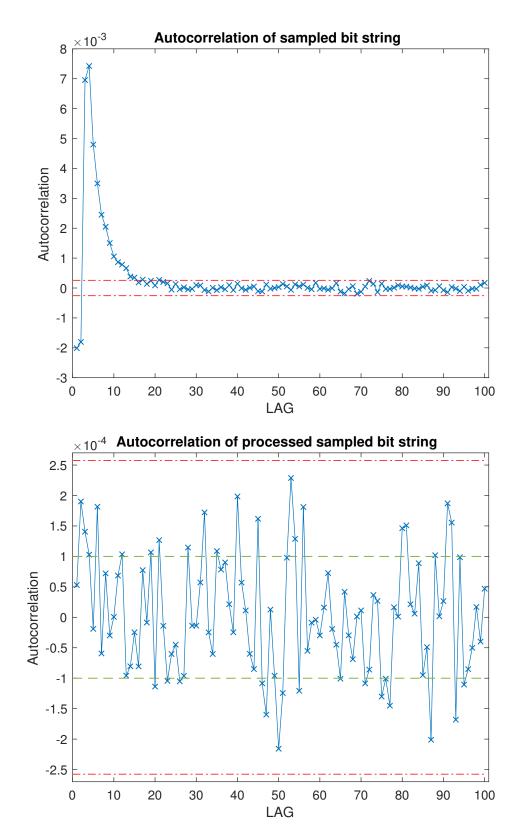

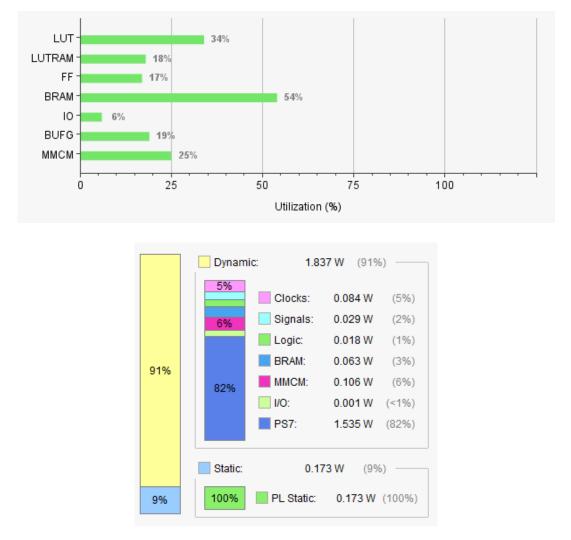

| 5.5 | Randy autocorrelation plots                                | 48 |

| 5.6 | Randy autocorrelation plot after Peres                     | 49 |

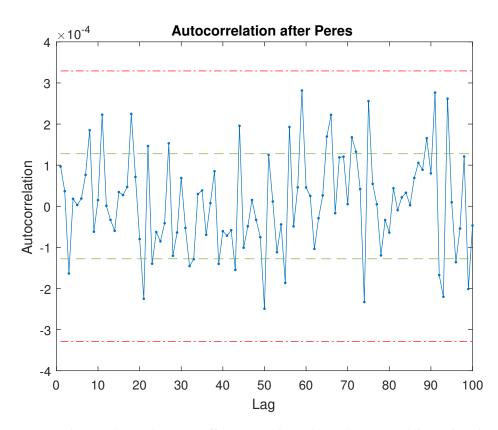

| 5.7 | Randy block diagram                                        | 52 |

| 5.8 | Randy Zynq-7000 utilization statistics                     | 54 |

| 5.9 | RandyApp main window view                                  | 56 |

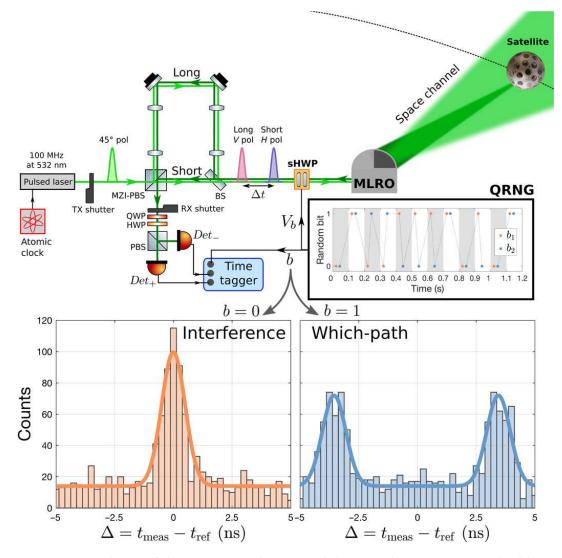

| 6.1 | Setup of Wheeler's delayed-choice experiment               | 59 |

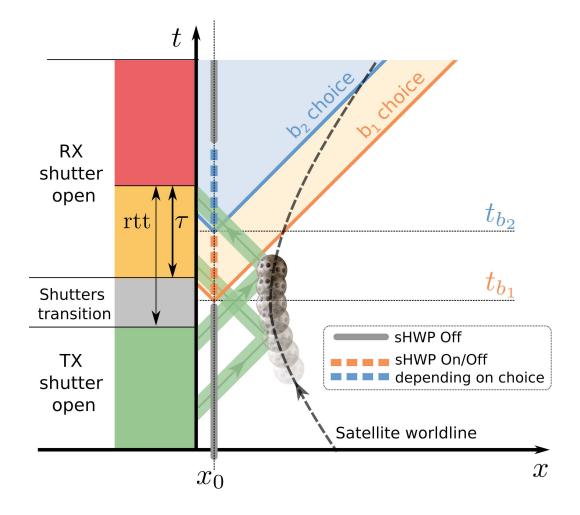

| 6.2 | Minkowski diagram                                          | 60 |

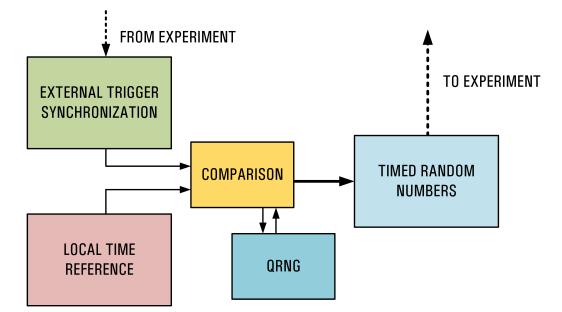

| 6.3 | Synchronization block schematic                            | 62 |

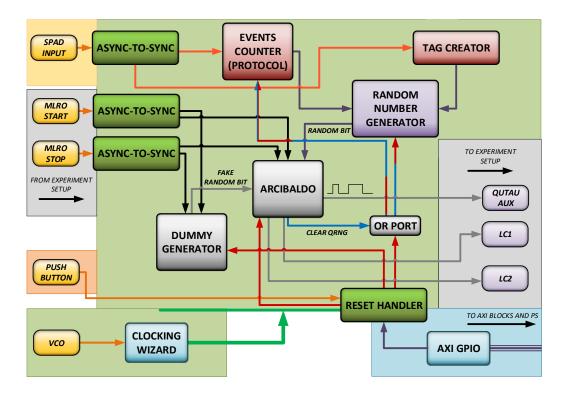

| 6.4 | Randy block design for Wheeler's delayed-choice experiment | 63 |

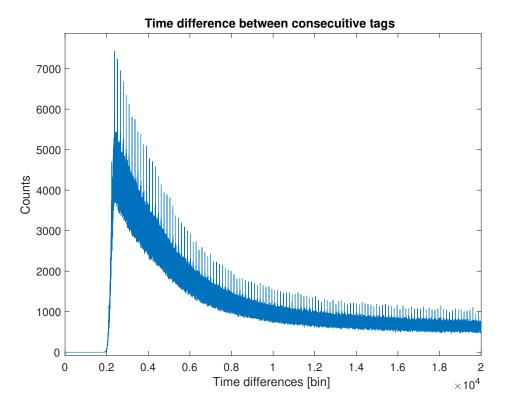

| 7.1 | LinoSPAD time difference distribution                      | 67 |

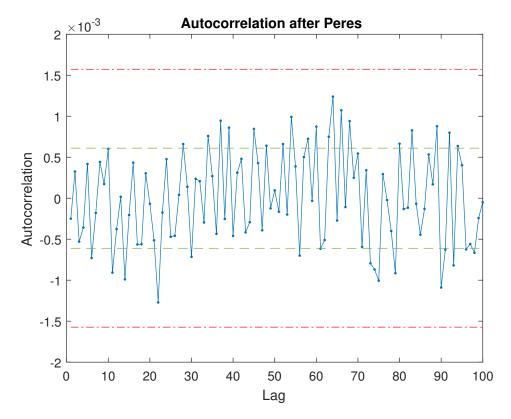

| 7.2 | LinoSPAD autocorrelation plot                              | 68 |

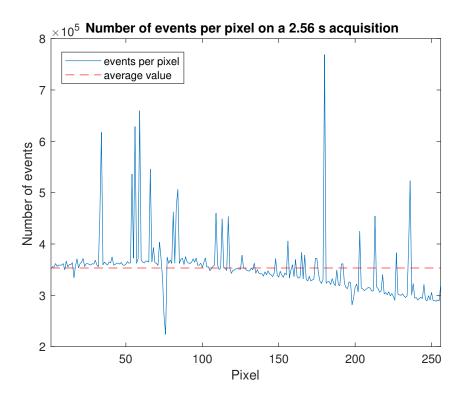

| 7.3 | LinoSPAD number of events for each pixel.                  | 69 |

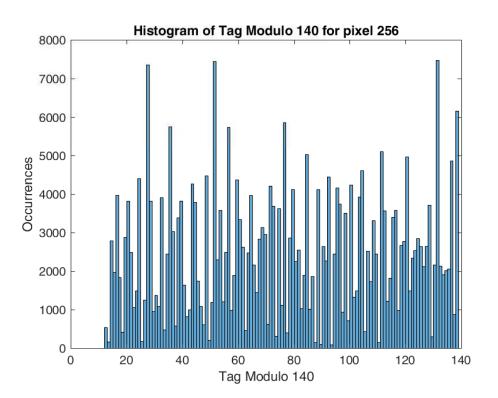

| 7.4 | Distribution of the tags modulo 140 for a single pixel     | 69 |

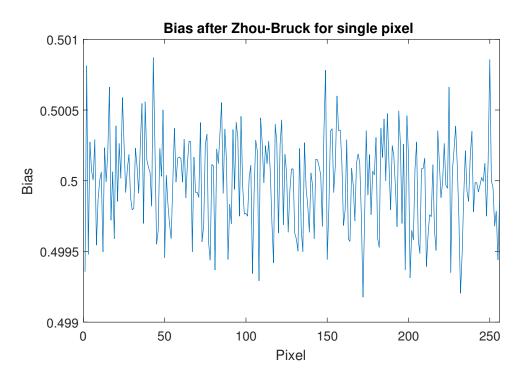

| 7.5 | Bias after the application of Zhou-Bruck method            | 71 |

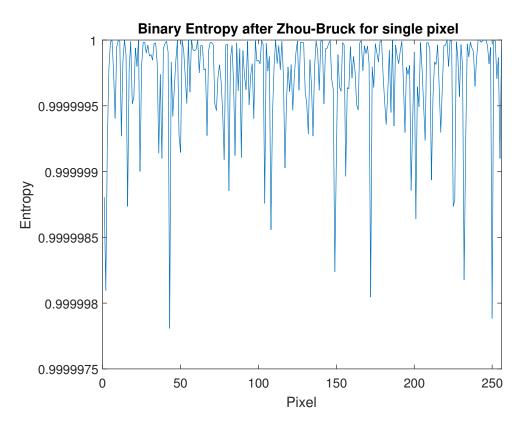

| 7.6 | Binary entropy after the application of Zhou-Bruck method  | 71 |

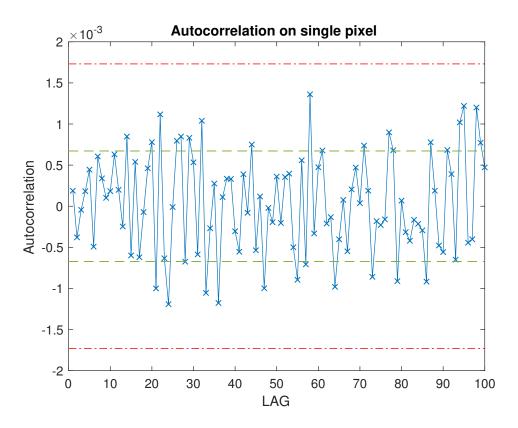

| 7.7 | Autocorrelation after the application of Zhou-Bruck method | 72 |

| 7.8 | QRNGs rate comparison                                      | 73 |

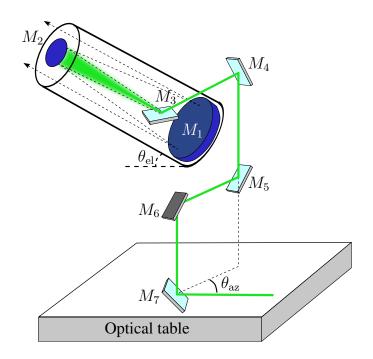

| 9.1  | Micius passage                                |

|------|-----------------------------------------------|

| 9.2  | Coudé path                                    |

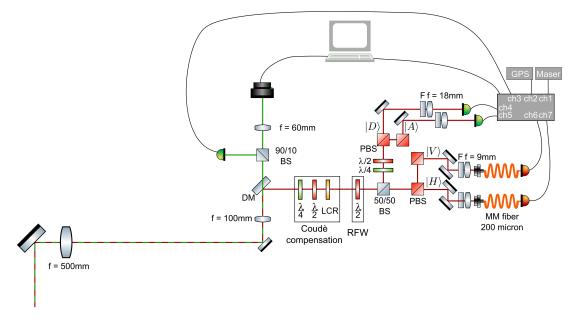

| 9.3  | Micius receiver optical setup                 |

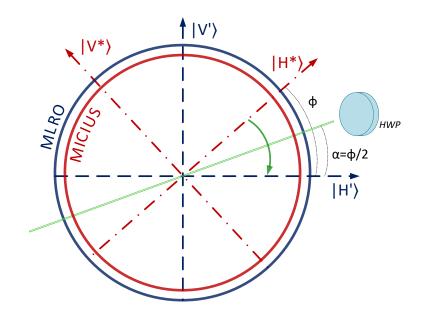

| 9.4  | Compensation of Micius angle 89               |

| 9.5  | Thorlabs KDC101         90                    |

| 9.6  | Thorlabs PRM1Z8         90                    |

| 9.7  | Thorlabs LCC25         91                     |

| 9.8  | Thorlabs device controller main window view   |

| 9.9  | Thorlabs device controller software structure |

| 9.10 | Thunderbolt GPS receiver    94                |

| 9.11 | Quntroller lock-to-UTC procedure    97        |

| 9.12 | Micius QBER plot and degree of polarization   |

| 10.1 | Setup of free-space QKD                       |

| 10.2 | Transmitter setup of free-space QKD           |

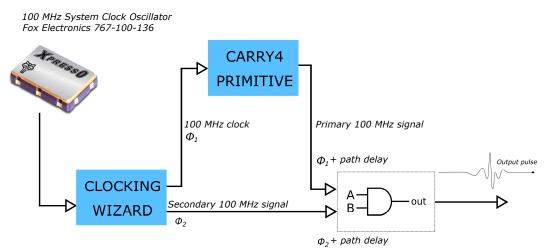

| 10.3 | Logic schematic for 350 ps pulse generation   |

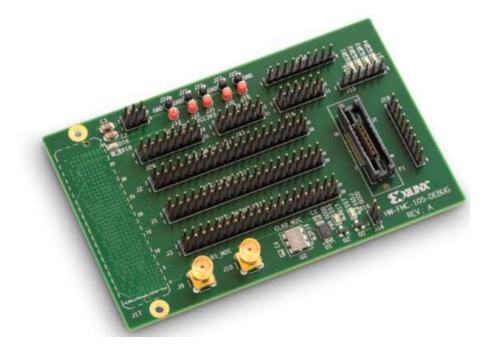

| 10.4 | XM105 debug card                              |

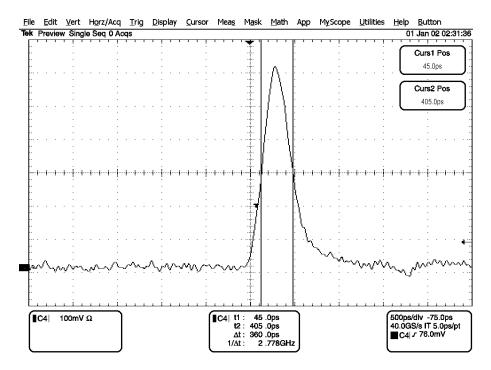

| 10.5 | 360 ps electrical pulse                       |

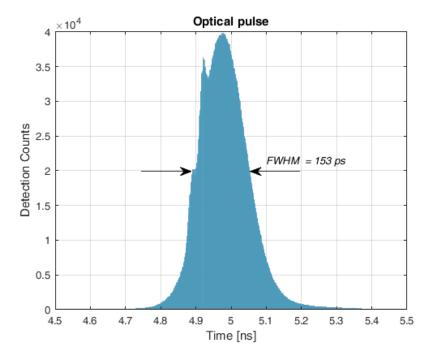

| 10.6 | 150 ps optical pulse                          |

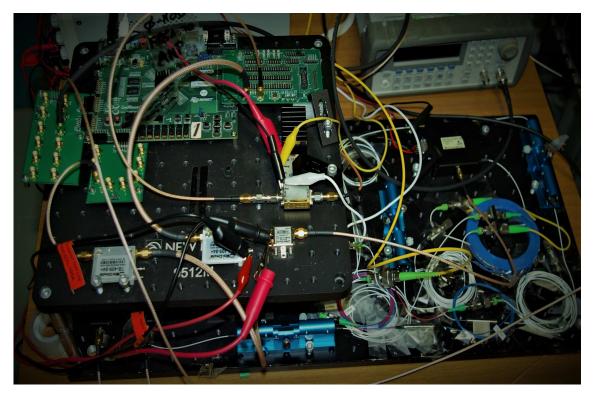

| 10.7 | Photograph of the QKD source                  |

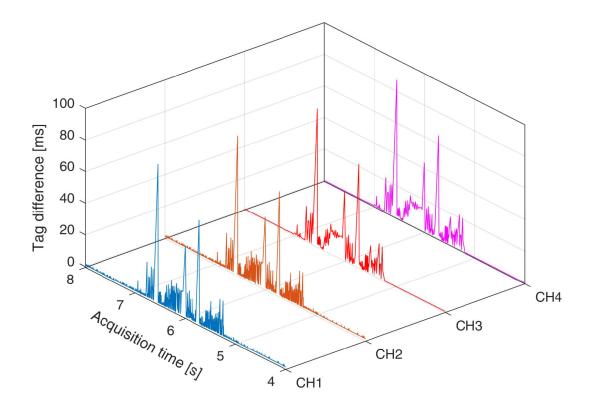

| A.1  | View of quTAU tag differences                 |

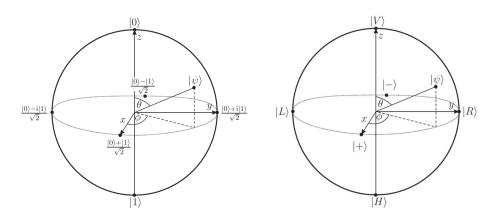

| B.1  | Bloch and Poincarè spheres                    |

## **List of Tables**

| 4.1 | Zhou-Bruk example table                | 38  |

|-----|----------------------------------------|-----|

| 8.1 | BB84 bit encoding lookup table         | 80  |

| A.1 | Result of tests                        | 109 |

| A.2 | Ratio computed from the previous table | 110 |

# **List of Abbreviations**

| AXIAgenzia Spaziale ItalianaAXIAdvanced eXtensible InterfaceBELBasic ELementCLBConfigurable Logic BlockDTDead TimeFMFaraday MirrorFPGAField Programmable Gate ArrayFSMGlobal Positioning SystemGUIGraphical User InterfaceHDLHardware Description LanguageIDEIntegrated Development EnvironmentLUTLookUp TableMIROMatera Laser Ranging ObservatoryMZINetwork Time ProtocolPMFPolgarammable LogicPMFPolgarammable LogicPMFQuantum Bit Error RateQBERQuantum InformationQKDQuantum Key DistributionRTMSimple Network Time ProtocolSNTPSimple Network Time ProtocolSNTPSimple Network Time ProtocolSNTPSimple Network Time ProtocolSNTPSingle Photon Avalanche DiodeSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationVHDLVHSIC Hardware Description Language                                                                                                                                                                                                                                                                                       | AP   | Afterpulse                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------|

| BELBasic ELementCLBConfigurable Logic BlockCLBDead TimeFMFaraday MirrorFMField Programmable Gate ArrayFPGAField Programmable Gate ArrayGMGlobal Positioning SystemGUIGraphical User InterfaceHDLHardware Description LanguageIDEIntegrated Development EnvironmentLUTLookUp TableMLROMatera Laser Ranging ObservatoryMZIMach-Zehnder InterferometerPMFPolarization Maintaining FiberPMFPolarization Maintaining FiberPMSQuantum Bit Error RateQBERQuantum InformationQKDQuantum Random Number GenerationRTTSimple Network Time ProtocolSNTPSimple Network Time ProtocolSNTPSingle Photon Avalanche DiodeSPADSingle Photon ProtocolFMFSingle Photon ProtocolCITGingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationFMFSingle Photon DetectorFMFSingle Photon DetectorFMFSingle Photon ProtocolFMFSingle Photon Protocol                                                                                                                                                                                                                                 | AXI  | Agenzia Spaziale Italiana           |

| CLBConfigurable Logic BlockDTDead TimeFMFaraday MirrorFPGAField Programmable Gate ArrayFSMFinite State MachineGPSGlobal Positioning SystemGUIGraphical User InterfaceHDLHardware Description LanguageIDEIntegrated Development EnvironmentLUTLookUp TableMLROMatera Laser Ranging ObservatoryMZIMach-Zehnder InterferometerNTPNetwork Time ProtocolPLProgrammable LogicPMFPolarization Maintaining FiberPRSQuantum Bit Error RateQIQuantum InformationQKDQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSPADSingle Photon Avalanche DiodeSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationCDCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                       | AXI  | Advanced eXtensible Interface       |

| DTDead TimeFMFaraday MirrorFPGAField Programmable Gate ArrayFPGAFinite State MachineGPSGlobal Positioning SystemGUIGraphical User InterfaceHDLHardware Description LanguageIDEIntegrated Development EnvironmentLUTLookUp TableMLROMatera Laser Ranging ObservatoryMZINetwork Time ProtocolPLProgrammable LogicPMFPolarization Maintaining FiberPMSQuantum Bit Error RateQBERQuantum Key DistributionQKDQuantum Key DistributionRTTSimple Network Time ProtocolSNTPSimple Network Time ProtocolSNTPSimple Network Time ProtocolSNTPSimple Network Time ProtocolSNTPSingle Photon Avalanche DiodeSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationTCPSingle Photon DetectorTCPSingle Photon Detector                                 | BEL  | Basic ELement                       |

| FMFaraday MirrorFPGAField Programmable Gate ArrayFSMFinite State MachineGDMGlobal Positioning SystemGUIGraphical User InterfaceHDLHardware Description LanguageIDEIntegrated Development EnvironmentLUTLookUp TableMLROMatera Laser Ranging ObservatoryMZINetwork Time ProtocolPMFPolarization Maintaining FiberPMFPolaer SecondPMSQuantum Bit Error RateQIQuantum Random Number GenerationRTMSingle Photon Avalanche DiodeSNTPSingle Network Time ProtocolSNTPSingle Photon Avalanche DiodeSPADGingle Photon DetectorFMASingle Photon DetectorFMASingle Photon DetectorFMASingle Photon SenerationICCTransmission Control ProtocolFMASingle Photon SenerationFMASingle Photon SenerationFMASin                            | CLB  | Configurable Logic Block            |

| FPGAField Programmable Gate ArrayFSMFinite State MachineGPSGlobal Positioning SystemGUIGraphical User InterfaceHDLHardware Description LanguageIDEIntegrated Development EnvironmentLUTLookUp TableMLROMatera Laser Ranging ObservatoryMZINetwork Time ProtocolPLProgrammable LogicPMFPolarization Maintaining FiberPSQuantum Bit Error RateQBERQuantum Key DistributionQKMQuantum Key DistributionRTMSimple Network Time ProtocolSNTPSimple Network Time ProtocolSNTPSingle Photon Avalanche DiodeSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationTCPSingle Photon DetectorTCPSingle Photon DetectorTCPFransmission Control ProtocolTRNGKandom Number GenerationTCPSingle Photon DetectorTCPSingle Photon DetectorTCPFransmission Control ProtocolTRNGKandom Number GenerationTCPSingle Photon DetectorTCPFransmission Control ProtocolTCPFransmission Control ProtocolTCPFransmission Control ProtocolTCPFransmission Control ProtocolTCPFransmission Control ProtocolTCPFransmission Control ProtocolTCPFransmission Control ProtocolTCPFra | DT   | Dead Time                           |

| FSMFinite State MachineGPSGlobal Positioning SystemGUIGraphical User InterfaceHDLHardware Description LanguageIDEIntegrated Development EnvironmentLUTLookUp TableMLROMatera Laser Ranging ObservatoryMZIMach-Zehnder InterferometerNTPNetwork Time ProtocolPLPolarization Maintaining FiberPMFPolarization Maintaining FiberPMSQuantum Bit Error RateQIQuantum Key DistributionQKDQuantum Random Number GenerationRTTSingle Photon Avalanche DiodeSNTPSingle Photon DetectorSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FM   | Faraday Mirror                      |

| GPSGlobal Positioning SystemGUIGraphical User InterfaceHDLHardware Description LanguageIDEIntegrated Development EnvironmentLUTLookUp TableMLROMatera Laser Ranging ObservatoryMZIMach-Zehnder InterferometerPMFPolgrammable LogicPMFPolarization Maintaining FiberPMFPolarization Maintaining FiberPMSQuantum Bit Error RateQBERQuantum InformationQKDQuantum Key DistributionRTTSimple Network Time ProtocolRTMSimple Network Time ProtocolPARGuantum Chrip TimeSNTPSimple Network Time ProtocolSNTPSingle Photon Avalanche DiodeSPADSingle Photon ProtocolSPADSingle Photon ProtocolTCPTransmission Control ProtocolTRNGTrue Random Number GenerationCOCHSocSINGLE Photon Avalanche DiodeSPDSingle Photon Avalanche DiodeSPDSingle Photon ProtocolSPDSingle Photon ProtocolSPNSingle Photon StructSPDSingle Photon ProtocolSPDSingle Photon StructSPDSingle Photon StructSPD                                          | FPGA | Field Programmable Gate Array       |

| GUIGraphical User InterfaceHDLHardware Description LanguageIDEIntegrated Development EnvironmentLUTLookUp TableMLROMatera Laser Ranging ObservatoryMZIMach-Zehnder InterferometerNTPNetwork Time ProtocolPLPolarization Maintaining FiberPMFPolarization Maintaining FiberPSProcessing SystemQBERQuantum InformationQKDQuantum Key DistributionRTTRound Trip TimeSNTPSimple Network Time ProtocolSNTPSingle Photon Avalanche DiodeSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FSM  | Finite State Machine                |

| HDLHardware Description LanguageHDEIntegrated Development EnvironmentLUTLookUp TableMLROMatera Laser Ranging ObservatoryMZIMach-Zehnder InterferometerNTPNetwork Time ProtocolPLProgrammable LogicPMFPolarization Maintaining FiberPSProcessing SystemQBERQuantum Bit Error RateQIQuantum Key DistributionQRNGQuantum Random Number GenerationRTTSimple Network Time ProtocolSNTPSingle Photon Avalanche DiodeSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GPS  | Global Positioning System           |

| IDEIntegrated Development EnvironmentLUTLookUp TableMLROMatera Laser Ranging ObservatoryMZIMach-Zehnder InterferometerNTPNetwork Time ProtocolPLProgrammable LogicPMFPolarization Maintaining FiberPPSPulse Per SecondPSProcessing SystemQBERQuantum Bit Error RateQIQuantum Key DistributionQKDQuantum Random Number GenerationRTTSimple Network Time ProtocolSNTPSingle Photon Avalanche DiodeSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GUI  | Graphical User Interface            |

| LUTLookUp TableMLROMatera Laser Ranging ObservatoryMZIMach-Zehnder InterferometerNTPNetwork Time ProtocolPLProgrammable LogicPMFPolarization Maintaining FiberPPSPulse Per SecondPSProcessing SystemQBERQuantum Bit Error RateQIQuantum InformationQKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTSimple Network Time ProtocolSoCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | HDL  | Hardware Description Language       |

| MLROMatera Laser Ranging ObservatoryMZIMach-Zehnder InterferometerMTPNetwork Time ProtocolNTPNetwork Time ProtocolPLProgrammable LogicPMFPolarization Maintaining FiberPPSPulse Per SecondPSProcessing SystemQBERQuantum Bit Error RateQIQuantum InformationQKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSOCSystem on a ChipSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IDE  | Integrated Development Environment  |

| MZIMach-Zehnder InterferometerNTPNetwork Time ProtocolPLProgrammable LogicPMFPolarization Maintaining FiberPPSPulse Per SecondPSProcessing SystemQBERQuantum Bit Error RateQIQuantum InformationQKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSoCSystem on a ChipSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LUT  | LookUp Table                        |

| NTPNetwork Time ProtocolPLProgrammable LogicPMFPolarization Maintaining FiberPMFPulse Per SecondPSProcessing SystemQBERQuantum Bit Error RateQIQuantum InformationQKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTSimple Network Time ProtocolSNTPSingle Photon Avalanche DiodeSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGCoordinated Universal TimeUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MLRO | Matera Laser Ranging Observatory    |

| PLProgrammable LogicPMFPolarization Maintaining FiberPMFPulse Per SecondPSProcessing SystemQBERQuantum Bit Error RateQIQuantum InformationQKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSOCSystem on a ChipSPADSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MZI  | Mach-Zehnder Interferometer         |

| PMFPolarization Maintaining FiberPPSPulse Per SecondPSProcessing SystemQBERQuantum Bit Error RateQIQuantum InformationQKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSoCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | NTP  | Network Time Protocol               |

| PPSPulse Per SecondPSProcessing SystemQBERQuantum Bit Error RateQIQuantum InformationQKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSoCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PL   | Programmable Logic                  |

| PSProcessing SystemQBERQuantum Bit Error RateQIQuantum InformationQKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSOCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PMF  | Polarization Maintaining Fiber      |

| QBERQuantum Bit Error RateQIQuantum InformationQKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSoCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PPS  | Pulse Per Second                    |

| QIQuantum InformationQKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSoCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PS   | Processing System                   |

| QKDQuantum Key DistributionQRNGQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSoCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | QBER | Quantum Bit Error Rate              |

| QRNGQuantum Random Number GenerationRTTRound Trip TimeSNTPSimple Network Time ProtocolSoCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | QI   | Quantum Information                 |

| RTTRound Trip TimeSNTPSimple Network Time ProtocolSoCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | QKD  | Quantum Key Distribution            |

| SNTPSimple Network Time ProtocolSoCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | QRNG | Quantum Random Number Generation    |

| SoCSystem on a ChipSPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RTT  | Round Trip Time                     |

| SPADSingle Photon Avalanche DiodeSPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SNTP | Simple Network Time Protocol        |

| SPDSingle Photon DetectorTCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SoC  | System on a Chip                    |

| TCPTransmission Control ProtocolTRNGTrue Random Number GenerationUTCCoordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SPAD | Single Photon Avalanche Diode       |

| <b>TRNG</b> True Random Number Generation <b>UTC</b> Coordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SPD  | Single Photon Detector              |

| UTC Coordinated Universal Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ТСР  |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TRNG | True Random Number Generation       |

| VHDL VHSIC Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UTC  |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VHDL | VHSIC Hardware Description Language |

### Introduction

*Quantum Information* (QI) finds its roots in the previous century but only in the last decade most of its applications have reached the notoriety. Quantum Random Number Generation (QRNG) and Quantum Key Distribution (QKD) are two of the most promising applications of QI. QRNG allows to produce true random numbers that can be used in many different fields like lotteries, Montecarlo analysis, cryptography and quantum mechanics experiments. As a matter of fact, the validity of such application relies on true randomness. Nowadays, the realization of a QRNG device does have reasonable costs and can be implemented through different technological solutions. This is the reason why QRNG, at this moment, is almost ready for a massive commercial spreading. On the other hand, QKD promises to solve every cryptographic issues in telecommunication. In principle, it can guarantee unconditional security over every transmission, i.e. an external attacker indeed has no chances to decrypt the secret message. Nevertheless, the practical realization of a QKD system requires expensive parts and fine calibrations which anyway allows limited key bit rate. Moreover, bringing the QKD in every day communications implies the building of dedicated infrastructures, which requires the involvement of different institutions and organizations outside the academic world. Therefore, QKD is yet to be consider a usable technology. The next 10-year challenge is to break through these hindrances and claim the QKD as the worldwide adopted cryptographic paradigm. In this framework, satellite QKD truly plays a major role since it can give a turn in the arrangement of the worldwide QKD net.

Such scientific investigations, which aim at the achievement of new accomplishments, often go hand in hand with the creation of new technological solutions which meet the needs of the investigation itself. Thus, the realization of QRNG and QKD systems relies on the design of dedicated technological supports. *Field Programmable Gate Array* (FPGA) gives the possibility to deal with the hardware at low level and to have full control over any apparatus. In fact, it becomes more and more essential to most of the high precision scientific experiments. Moreover, its integration with a software counterpart, the so-called *System on a Chip* (SoC), is indeed a matter of fact and gives almost no limits to what can be done. The integration between hardware and software is also exploited by many different commercial devices which are designed for advanced and cutting-edge applications. The programming and calibration of such devices can also be essential to scientific investigations.

This thesis work represents a linking point between these two aforementioned topics: hardware and software systems at the service of Quantum Information.

The work is divided in three parts: Part I describes the basics of the hardware and software designs that were used in the QI applications; Part II focuses on two different QRNG applications while Part III on two different QKD applications.

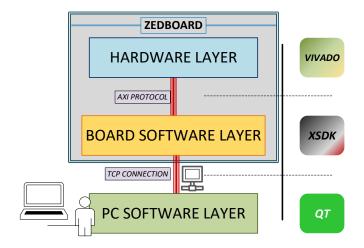

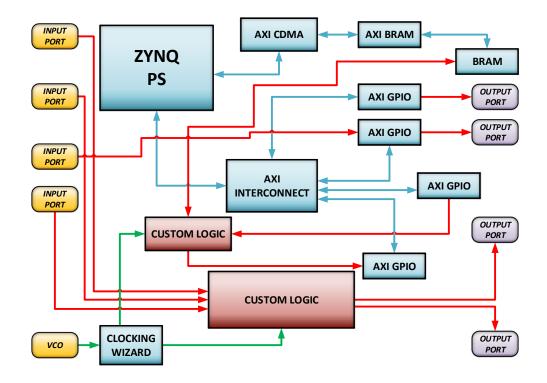

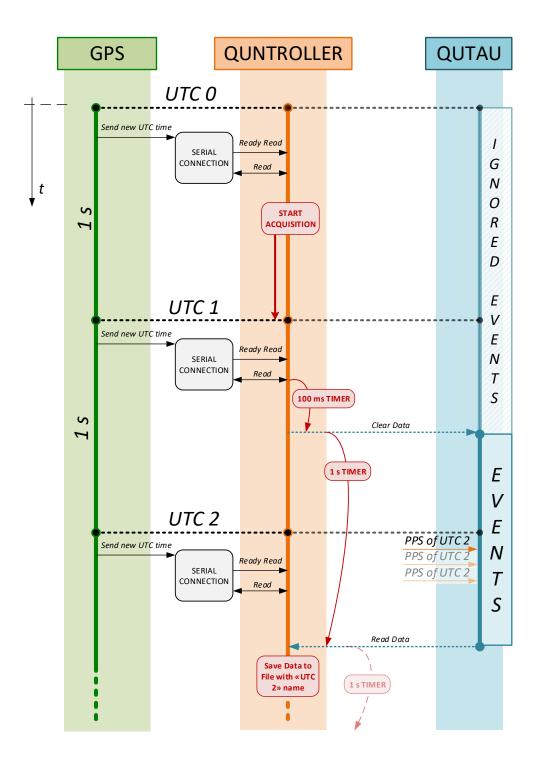

In Part I, chapter 1 gives a brief description of the FPGA and SoC technologies along with a description of the ZedBoard development board and the development enviroments (Vivado and SDK by Xilinx). In chapter 2 the main structure design and the development solutions are described. The system will be adapted to a QRNG application, described in chapter 5, and to the Wheeler's delayed-choice experiment for the investigation of the quantum nature of light. In chapter 3 an introduction on the quTAU TDC device is given along with the description of a performing management software, Quntroller, developed on Qt IDE. This software will be used for the satellite QKD experiment described in chapter 9.

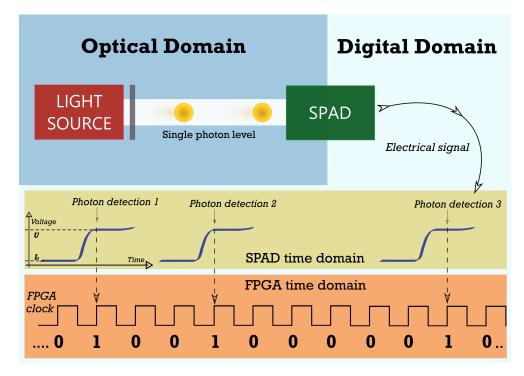

Part II talks about Quantum Random Number Generation applications. Chapter 4 introduces the topic and explains some of the generation protocols, based on the photon time of arrival, and algorithms that can be used to produce random numbers. In chapter 5 the QRNG device called *Randy* is described. The device is FPGA-based and was realized from the ZedBoard system described in chapter 2. Its optical setup comprehends a light source attenuated to single-photon level and a single-photon avalanche diode (SPAD) which output is sampled by the board. The device allows to choose among different protocols and to have a full control over the generation process. A new generation approach is investigated and applies the Peres unbiasing algorithm directly to the sampled string after the treatment of SPAD non idealities known as deat time and afterpulse. Under the condition of a photon rate equivalent to 200 kcounts/s and a sampling rate of 100 MHz, this approach led to a final bit rate of 1.8 Mbit/s. Through a dedicated modification, the real time feature of Randy was used to generate timed random numbers used to set specific optical components in the Wheeler's delayed-choice experiment extended to space. The experiment, described in chapter 6, was part of a collaboration with the Agenzia Spaziale Italiana (ASI) and was realized at the Matera Laser Ranging Observatory (MLRO). The experiment investigated the dual nature of light through the realization of a Mach-Zehnder interferometer (MZI) extended to space. Chapter 7 describes the analysis conducted on a second device, LinoSPAD, produced by the AQUA lab at Delft University & EPFL. The device features 256 CMOS-SPAD pixels arranged in four linear array of 64 pixels each as well as an FPGA TDC which gives a time precision of  $\sim$ 17.9 ps. A dedicated post-processing procedure was developed to exploit LinoSPAD as a QRNG. Such procedure, based on the Peres and Zhou-Bruk algorithms, takes into account the presence of known SPAD non idealities and also deals with the FPGA TDC non linear behavior. The final generation bit rate is equivalent to 300 Mbit/s.

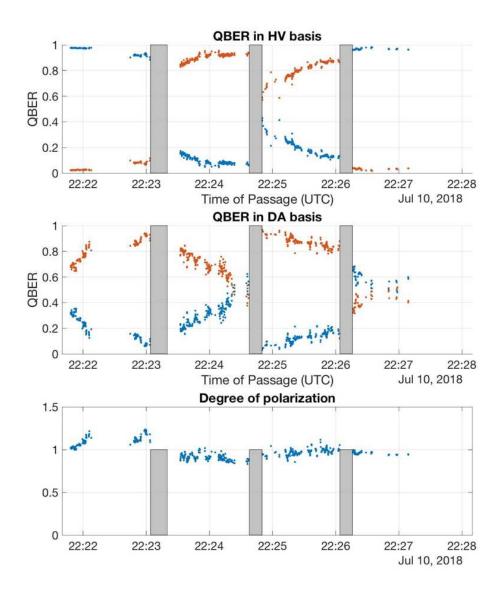

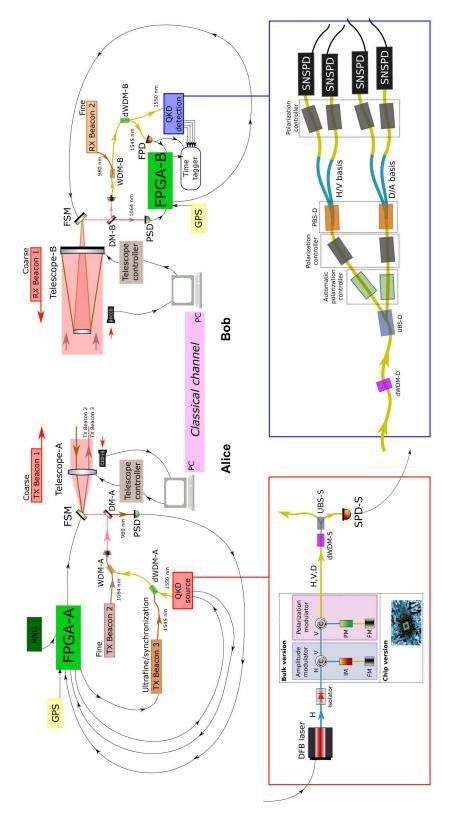

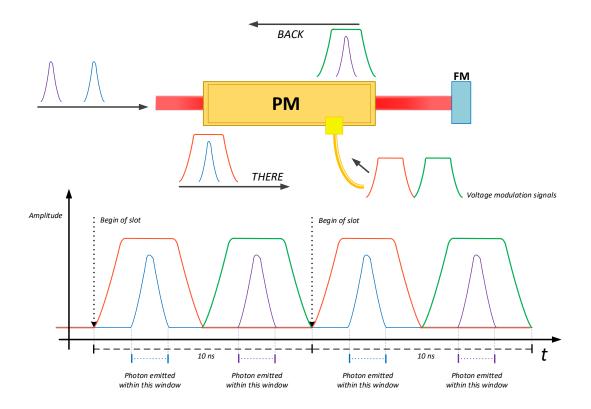

Part III is dedicated to the description of two QKD applications. The first one is part of a collaboration with ASI and the Chinese Academy of Sciences (CAS) and is described in chapter 9. The objective is the realization of a QKD link between the Chinese satellite Micius and MLRO. A preliminary test was conducted in July 2018 to investigate the feasibility of such link and the capability to distinguish between a light polarization and another. The test required a proper setting of the Quntroller software for acquiring the significant data from the setup. The software was also updated to synchronized the acquisition to the UTC time, which required a dedicated GPS receiver. Moreover, a brand new software was developed in order to keep the optical axis alignment between Micius satellite and the MLRO telescope. The software controlled electro-optomechanical and electro-optical components which implemented a time-variant compensation of the beam angular changes through the optical path. The second application is described in chapter 10. The main objective is to realize a full free-space QKD system over a distance of tenths of kilometers through the synthesization of qubits as polarized single photons. The project was developed by the Quantum Future group as a whole and required the design of various parts in order to implement the QKD system from A to Z. The chapter only describes a dedicated design developed for the FPGA board, once again the Zed-Board, at the transmitter. In the QKD source, the qubit is produced by a DFB laser attenuated to single-photon level which is driven by an electrical signal from the FPGA. Since the optical pulse width is directly proportional to the electrical pulse width, a smart FPGA design is used to shorten this width and thus reduce the time slot which the photon is emitted in. From two 100 MHz signals is produced a 350 ps pulse which is at the limit of the physical analog bandwidth of the board. As a directly consequence, a shorter time slot implies a better capability to discriminate the qubit over the background noise leading to a lower QBER and hence to a higher secret key bit rate. Similar techniques are applied to drive the electro-optical phase and intensity modulator to set the photon polarization and implement the *decoy*.

## Part I

# Hardware and software designs

### Chapter 1

### SoC system and related tools

This chapter gives an introduction to FPGA and SoC technology and the ZedBoard development board. It also gives an overview of the software tools and technical knowledge used to program and design the board.

#### 1.1 Introduction to FPGA and SoC

Field Programmable Gate Array (FPGA) technology was born in 1980s and allows the configuration of an electronic circuit through an Hardware Description Language (HDL). It comprehends a fabric of Configurable Logical Blocks (CLBs) embedded in a huge array of interconnecting wiring. Usually, CLBs contain logic elements like Lookup Tables (LUTs), multiplexers, flip-flops and memory elements. The configuration program is stored in a dedicated memory which can be SRAM, Antifuse or EPROM [1]. The invention of FPGA is generally attributed to Ross Freeman [2] who was co-founder of Xilinx company in 1984. FPGA is considered to be an evolution of prior Programmable Logic Device (PLD) technologies developed during the 1970s [3, Chapter 11]. During the 1990s, FPGA was mainly used for telecommunication and networking applications and then it rapidly spread into industrial and consumer ones. At the end of 2000s the CPU evolution trend found one of its limits. Increasing the clock frequency in order to achieve higher performances was not possible anymore: power consumption started to become way too high and other solutions needed to be investigated. While GPU technology could indeed represent a solution offering powerful advantages, FPGA technology had a major spread thanks to its high computational power and task-parallelization keeping its power consumption within reasonable limits [4, 5]. Furthermore, boards with FPGA chip began to integrate additional technologies, which enlarged its range of possible applications and brought it into contact with new users communities. A huge achievement was the integration of FPGA and CPU which brought together the best of both worlds: high performances along with the easiness to integrate huge softwares. This solution is part of the System on a Chip (SoC) category and today is universally adopted [6–9]. A valid alternative is represented by the so-called Soft-Core processors which are hardware-described-processors implemented directly on an FPGA chip [10]. Microblaze and Picoblaze are two well-known examples of this technology [11–13]. Although they can be customized for specific applications and thus shortner task-to-complete time, they also require additional design efforts and do not have the high level flexibility of SoC. Furthermore, the power consumption can also be an issue. For a complete comparison between these two technologies please refer to [14]. Since our applications do not require particular or critical processor functionalities, SoC was preferred over Soft-Core.

The two main producers of FPGA chip are *Xilinx* company and *Intel-Altera* company; both offer a wide range of solutions fitting the applications required by the market. Nowadays, applications can vary from *cloud management* [15] to *high per*formances application for space environment [16, 17], from neural networks [18, 19] to machine learning [20, 21] and from cryptography [22-26] to random number generator [27–31]. One of the FPGA main advantages that can be exploited in the scientific investigation is its deterministic behavior. Every sequential operation defined in the design can be temporally described as a multiple of the time period of a *clock* signal. Within this framework, the term *latency* assumes a different meaning with respect to the software world: a general operation has a known latency perfectly defined and cannot change. Moreover, the magnitude order of such latency is well below the performances of any software-based technology. Therefore, this feature can have fundamental role in every application that requires very precise timing and synchronization. Moreover, the FPGA integration in a SoC gives the possibility to easily expand the number of tests that can be conducted on a setup since system parameters can be changed through the software counterpart.

#### 1.2 ZedBoard development board

At this moment, the FPGA boards market can offer a great variety of solutions. The cutting-edge technology is represented by the Ultrascale chip families which are realized in 16 and 20 nm process and offer the possibility to realize architectures with incredible computational power. Clearly, such solutions have a certain cost since they are usually mounted on dedicated board with high connectivity pin ports, large memories, transceiver modules and other high performance components. Nevertheless, these products can be an overkill for many applications. Hence, a low cost board could fit the specifications required for the realization of the first prototypes of the QRNG and QKD applications described in this work. Furthermore, the developed designs can be easily adapted to the Ultrascale architectures for future improvements of the applications. For this reason, the chosen board was the *ZedBoard* development board.

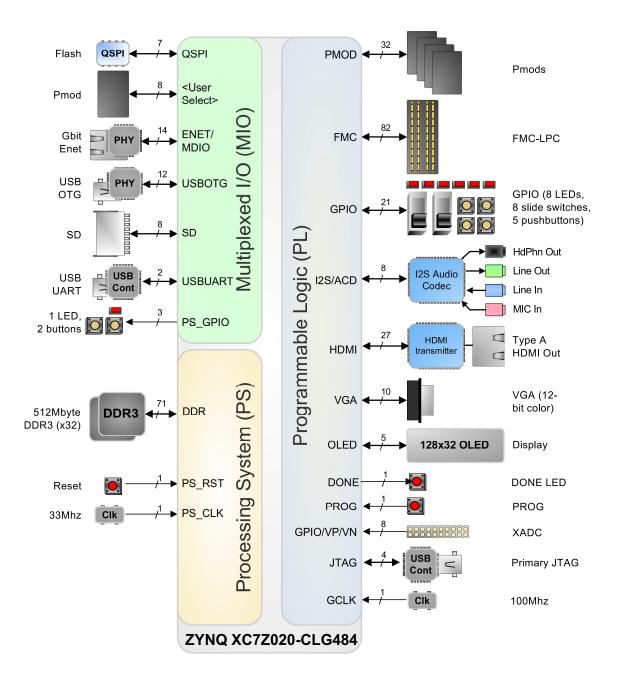

Released in 2013, the ZedBoard (figure 1.1) is a development kit produced by Avnet in collaboration with Digilent and Xilinx. Thanks to presence of the Zynq-7000 SoC which allows high flexibility and low costs, it has remarkably spread over the past few years and had a major role in different applications [32–34]. ZedBoard elements are listed below and illustrated in 1.2. For a full and detailed description see [35].

FIGURE 1.1: ZedBoard development kit. Picture by Digilent.

- Xilinx<sup>®</sup> XC7Z020-1CLG484C Zynq-7000 AP SoC

- Primary configuration = QSPI Flash

- Auxiliary configuration options

- \* Cascaded JTAG

- \* SD Card

- Memory

- 512 MB DDR3 (128M x 32)

- 256 Mb QSPI Flash

- Interfaces

- USB-JTAG Programming using Digilent SMT1-equivalent circuit

- \* Accesses PL JTAG

- \* PS JTAG pins connected through PS Pmod

- 10/100/1G Ethernet

- USB OTG 2.0

- SD Card

- USB 2.0 FS USB-UART bridge

- Five Digilent Pmod<sup>™</sup> compatible headers (2x6) (1 PS, 4 PL)

- One LPC FMC

- One AMS Header

- Two Reset Buttons (1 PS, 1 PL)

- Seven Push Buttons (2 PS, 5 PL)

- Eight dip/slide switches (PL)

- Nine User LEDs (1 PS, 8 PL)

- DONE LED (PL)

- On-board Oscillators

- 33.333 MHz (PS)

- 100 MHz (PL)

- Display/Audio

- HDMI Output

- VGA (12-bit Color)

- 128x32 OLED Display

- Audio Line-in, Line-out, headphone, microphone

- Power

- On/Off Switch

- 12V @ 5A AC/DC regulator

#### 1.2.1 Zynq-7000 chip

The Zynq-7000 is a SoC family produced by Xilinx company. It integrates ARMbased processor with an FPGA. The XC7Z020-1CLG484C mounted on the ZedBoard has a two-core ARM Cortex A9 and a 28 nm Artix-7 based programmable logic and comprehends 85 thousands logic cells, 200 DSP Slices and 200 I/O pins. These features are suitable for a wide range of applications. The FPGA part is also indicated as *Programmable Logic* (PL) while the CPU is indicated as *Processing System* (PS). This is the preferred nomenclature used throughout this work. Full description and specifications can be found on the official documentation [36, 37].

FIGURE 1.2: ZedBoard Block Diagram. Picture by Avnet.

#### **1.3 Vivado Design Suite**

Vivado Design Suite is a software suite developed by Xilinx [38] which allows the design of Xilinx FPGA-chip architecture. A chip project can be organized by using the useful *Block Design* which gives a schematic overview of the blocks interconnection and automatizes many procedures. The software offers full control over compilations passages, i.e. *Synthesis, Implementation* and *Bitstream Generation*. Furthermore, it includes several IP cores produced by Xilinx, which broadens the design possibilities.

#### 1.4 Xilinx SDK

The Xilinx Software Development Kit (XSDK) [39], also indicated as SDK, is a design environment for creating embedded applications. It is based on the Eclipse framework and allows to create standalone and OS-based applications to be run on a CPU counterpart of a Xilinx SoC. Standalone applications can be programmed in C or C++ language while the OS ones can be Linux-based or FreeRTOS-based [40].

#### 1.5 AXI Protocol

The Advanced eXtensible Interface protocol [41] is a part of ARM AMBA, which is a standard for the blocks connection, management and communication in SoC designs. The main aim is to make easier the handling and the development of multi-processor systems, its controllers and peripherals. This protocol is very robust and guarantees a safe and fast communication between different modules which are linked together with a master-slave interface system. AXI protocol is used by most of the Xilinx IP Cores represents a link between the SDK software with the Vivado hardware design: each AXI-based module has its own driver which can be initialized in the software code calling specific functions. Therefore, this protocol is fundamental for communication with hardware blocks.

#### **1.6 Finite State Machine**

A finite state machine, also indicated as FSM, is an important element in the design of sequential logical circuits. Basically, it shapes the behavior of the circuit abstracting from its *state* of operation. Therefore, the circuit moves from a state to another and performs a specific task depending on the state. Furthermore, it organizes the VHDL code in a more intuitive way making the code more readable and easier to understand. For this reason, most of the custom VHDL modules described throughout this work were designed with a dedicated finite state machine.

#### 1.6.1 Mealy and Moore state machine

There are two different types of state machine: Mealy state machine [42] and Moore state machine [43]. In the Mealy machine the output depends both on the state and the input, whereas the Moore one depends only on the state and not on the input. In general, the Mealy state machine requires less states (then less hardware) and can work faster than the Moore one. Nevertheless, its outputs can change asynchronously, which undermines the predictability of working, and its design might be complicated. Since the developed systems required a great accuracy in the execution of their functions and since there were no restrictions on the hardware usage and on the reactivity, only Moore state machines were used.

#### 1.6.2 Coding styles