Head office: Università degli studi di Padova Department of Information Engineering

Ph.D. School in Information Engineering

Curriculum: Information and Communication Science and

Technology (I.C.T)

Series XXXII

## Characterization and modeling of GaN-based transistors for power applications

Thesis written with the financial contribution of Fondazione Cariparo

**Coordinator:** Andrea Neviani **Supervisor:** Enrico Zanoni

Ph.D. Student: Matteo Borga

## **Table of Contents**

| Abstract    | I                                                 |

|-------------|---------------------------------------------------|

| Sommario.   | V                                                 |

| Introductio | n VII                                             |

| Chapter 1:  | Gallium Nitride and its applications1             |

| 1.1 Gal     | lium Nitride                                      |

| 1.1.1       | Crystal structure and band diagram4               |

| 1.1.2       | Polarization effects on GaN                       |

| 1.1.3       | Growth techniques                                 |

| 1.1.4       | Substrates for GaN growth                         |

| 1.2 Gal     | N-based Devices                                   |

| 1.2.1       | Lateral devices: HEMTs12                          |

| 1.2.2       | Vertical Devices: Trench Gate MOSFET15            |

| Chapter 2:  | Reliability of the GaN-on-Si vertical stack       |

| 2.1 Buf     | fer decomposition experiment19                    |

| 2.1.1       | Devices description                               |

| 2.1.2       | Leakage and breakdown analysis                    |

| 2.1.3       | Reliability of the AlN nucleation layer           |

| 2.2 Rel     | iability analysis on a full GaN-on-Silicon stack  |

| 2.2.1       | Devices description                               |

| 2.2.2       | Leakage analysis and step-stress tests            |

| 2.2.3       | Time dependent breakdown and reliability analyses |

| 2.2.4       | Electroluminescence (EL) and optical inspections  |

|          | 2.2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Outcomes of the analysis                                                                                                                                                                                                                                      |                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 2.       | 3 Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nclusions                                                                                                                                                                                                                                                     | 44                                                   |

| Cha      | pter 3:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Doping of substrates for GaN-on-Si Growth                                                                                                                                                                                                                     | 45                                                   |

| 3.       | 1 The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e role of the substrate resistivity                                                                                                                                                                                                                           | 47                                                   |

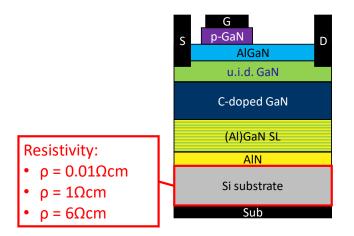

|          | 3.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Devices description                                                                                                                                                                                                                                           | 47                                                   |

|          | 3.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Vertical leakage and EMMI analysis                                                                                                                                                                                                                            |                                                      |

|          | 3.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Step-stress test and evidence of Vth shift                                                                                                                                                                                                                    | 52                                                   |

|          | 3.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Positive backgating transients                                                                                                                                                                                                                                | 55                                                   |

| 3.       | 2 TC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | AD analysis on AlN/Si junction                                                                                                                                                                                                                                | 60                                                   |

|          | 3.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Details on the measured and simulated structures                                                                                                                                                                                                              | 60                                                   |

|          | 3.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Two-diodes model                                                                                                                                                                                                                                              | 61                                                   |

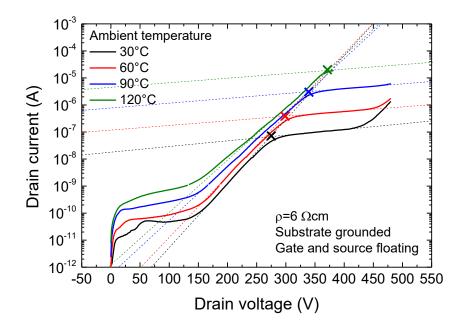

|          | 3.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Temperature and Si-doping dependences                                                                                                                                                                                                                         | 66                                                   |

|          | 3.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Extension to a full GaN-on-Silicon stack                                                                                                                                                                                                                      | 67                                                   |

| 3.       | 3 Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nclusions                                                                                                                                                                                                                                                     | 69                                                   |

| Cha      | pter 4:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GaN-based trench gate MOS devices                                                                                                                                                                                                                             | 71                                                   |

| 4.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                               |                                                      |

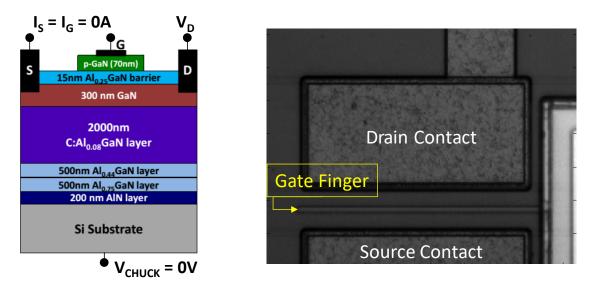

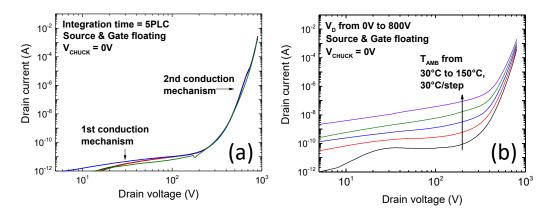

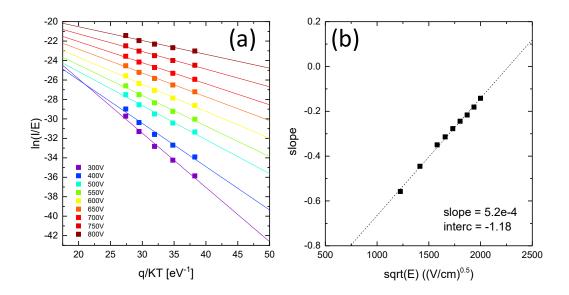

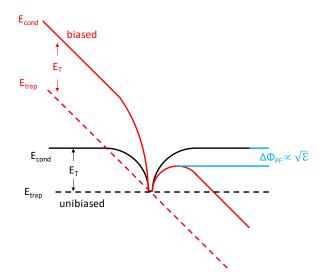

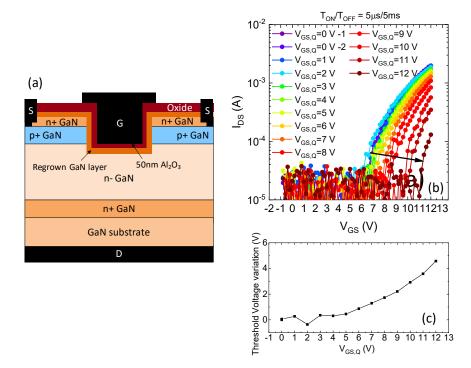

|          | 1 De                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | vices description                                                                                                                                                                                                                                             | 73                                                   |

| 4.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | vices description<br>te transport mechanisms                                                                                                                                                                                                                  | 73<br>77                                             |

| 4.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                             | 77                                                   |

| 4.       | 2 Ga                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | te transport mechanisms                                                                                                                                                                                                                                       | 77<br>77                                             |

| 4.       | 2 Ga<br>4.2.1<br>4.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | te transport mechanisms<br>Gate-Source, Gate-Drain and OFF-state characterization                                                                                                                                                                             | 77<br>77<br>83                                       |

|          | 2 Ga<br>4.2.1<br>4.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | te transport mechanisms<br>Gate-Source, Gate-Drain and OFF-state characterization<br>Gate dielectrics comparison                                                                                                                                              | 77<br>77<br>83<br>89                                 |

|          | 2 Ga <sup>.</sup><br>4.2.1<br>4.2.2<br>3 Ga <sup>.</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | te transport mechanisms<br>Gate-Source, Gate-Drain and OFF-state characterization<br>Gate dielectrics comparison<br>te capacitance                                                                                                                            | 77<br>77<br>83<br>89<br>89                           |

|          | 2 Ga<br>4.2.1<br>4.2.2<br>3 Ga<br>4.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | te transport mechanisms<br>Gate-Source, Gate-Drain and OFF-state characterization<br>Gate dielectrics comparison<br>te capacitance<br>Gate capacitance calculations                                                                                           | 77<br>77<br>83<br>83<br>89<br>                       |

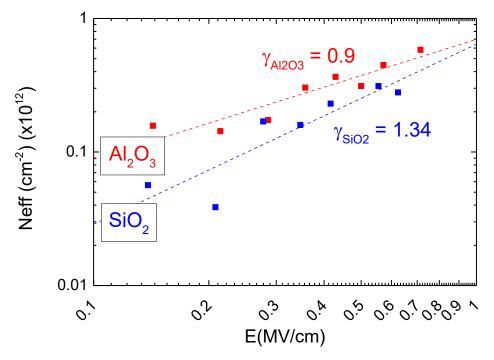

|          | 2 Ga<br>4.2.1<br>4.2.2<br>3 Ga<br>4.3.1<br>4.3.2<br>4.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | te transport mechanisms<br>Gate-Source, Gate-Drain and OFF-state characterization<br>Gate dielectrics comparison<br>te capacitance<br>Gate capacitance calculations<br>Gate CV measurement and modelling                                                      | 77<br>77<br>83<br>89<br>89<br>                       |

| 4.<br>4. | <ol> <li>2 Gat</li> <li>4.2.1</li> <li>4.2.2</li> <li>3 Gat</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.3</li> <li>4 Cot</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | te transport mechanisms<br>Gate-Source, Gate-Drain and OFF-state characterization<br>Gate dielectrics comparison<br>te capacitance<br>Gate capacitance calculations<br>Gate CV measurement and modelling<br>Dielectric trap density evaluation and comparison | 77<br>77<br>83<br>89<br>89<br>92<br>92<br>100<br>106 |

| 4.<br>4. | <ol> <li>2 Gat</li> <li>4.2.1</li> <li>4.2.2</li> <li>3 Gat</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.3</li> <li>4 Conspondent Strength Strengt Strength Strengt Strength Strength Strength Strength Strengt</li></ol> | te transport mechanisms<br>Gate-Source, Gate-Drain and OFF-state characterization<br>Gate dielectrics comparison<br>te capacitance<br>Gate capacitance calculations<br>Gate CV measurement and modelling<br>Dielectric trap density evaluation and comparison | 77<br>77<br>83<br>89<br>                             |

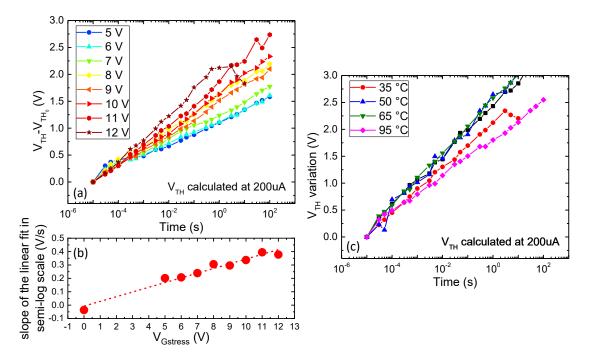

| 5.2 Application of the Vth transient setup 115                            |  |  |

|---------------------------------------------------------------------------|--|--|

| 5.2.1 µs-Range Evaluation of Threshold Voltage Instabilities of GaN-on-Si |  |  |

| HEMTs with p-GaN Gate [65] 115                                            |  |  |

| 5.2.2 Gate Stability and Robustness of In-Situ Oxide GaN Interlayer Based |  |  |

| Vertical Trench MOSFETs (OG-FETs) [66] 120                                |  |  |

| Conclusions                                                               |  |  |

| List of publications                                                      |  |  |

| References                                                                |  |  |

## Abstract

GaN-based devices have emerged as a promising solution for power management applications. The intrinsic physical properties of the Gallium Nitride are exploited in order to considerably improve the efficiency and to reduce the volume of the next generation power switching converters. The wide energy gap allows to fabricate high voltage-rate devices with a reduced area consumption, whereas the high mobility guarantees a considerably low on-Resistance of the transistor. Moreover, thanks to the reduced parasitic capacitances, the operating frequency of the devices can be higher than conventional Silicon based transistors.

In order to ensure a wide spreading of Gallium Nitride technology in the power transistors market, the price of the devices needs to be kept as low as possible. The costs of native substrates for the fabrication of GaN transistors are nowadays prohibitive, so that the epitaxial growth of Gallium Nitride on Silicon substrates has been developed. GaN-on-Silicon is the most suitable technology to fabricate GaN-based devices on a cheap and large area wafers (up to 200 mm), resulting in a significant reduction of the production costs.

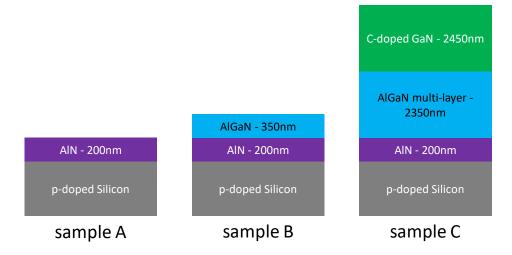

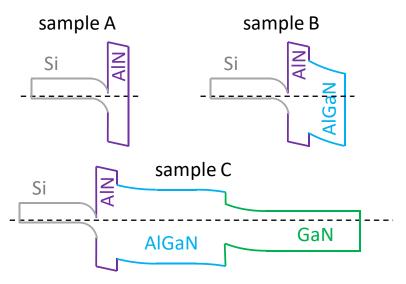

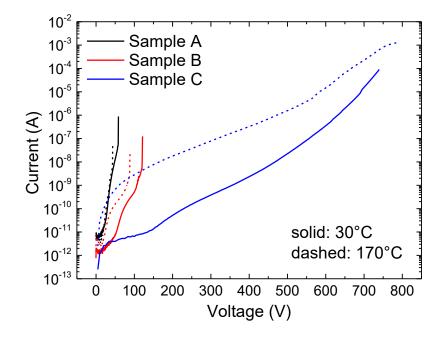

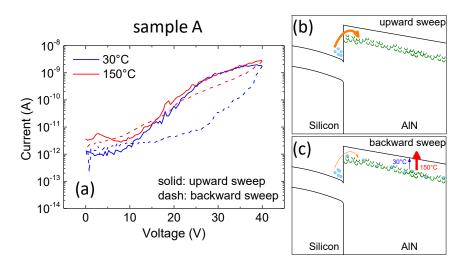

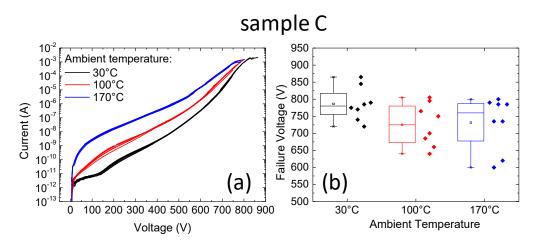

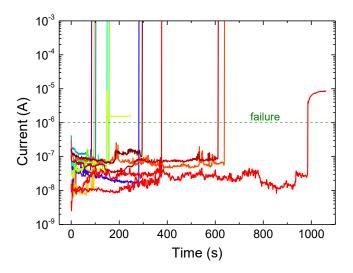

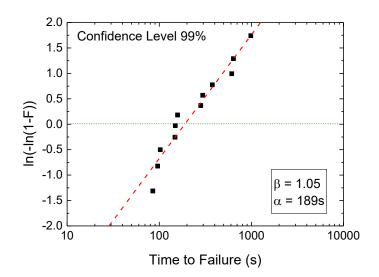

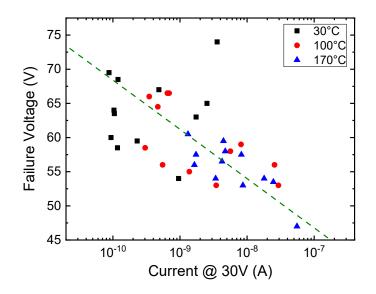

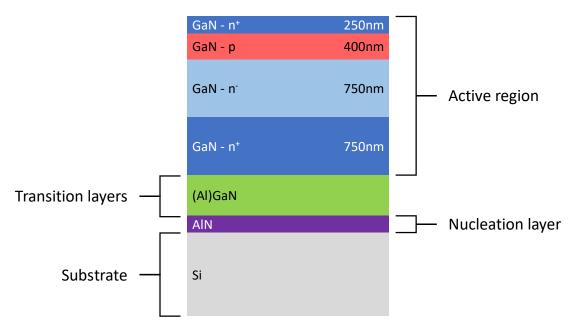

On the other hand, growing GaN on a foreign substrate results in high dislocation and defect densities which could affect the performance of the devices in terms of both losses and reliability issues. A so-called "buffer decomposition experiment" allowed to evaluate the role of the different layers which compose the vertical stack of a GaN-on-Silicon wafer by characterizing samples obtained by stopping the epitaxial growth at different stages of the process. It is demonstrated that both the thickness and the composition of the epitaxial stack, beside enhancing the breakdown voltage, improve the material quality by limiting the propagation of defects and dislocations. Moreover, a study on the reliability of the Aluminum Nitride layer grown on silicon is presented,

#### Abstract

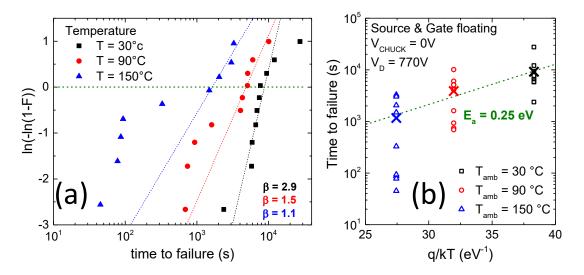

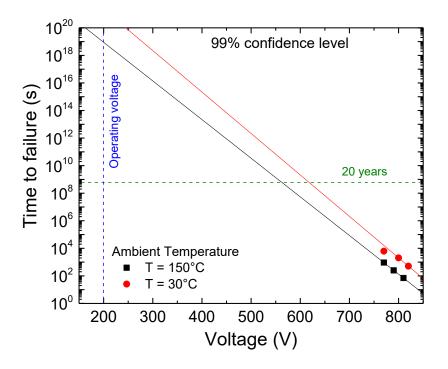

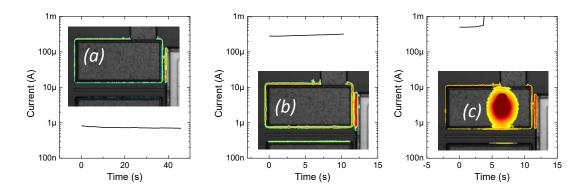

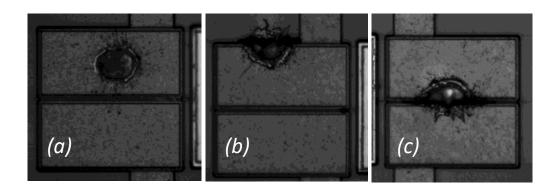

showing that the AlN fails due to a wear-out process following a Weibull distribution. Furthermore, an extensive analysis on the reliability of the GaN-on-Silicon vertical stack is presented, as well as a systematic study on the failure statistic. It is shown that the time to failure of the GaN-on-Silicon stack is Weibull distributed, and, although it is weakly temperature-activated, it exponentially depends on the applied voltage. Moreover, the expected lifetime of the tested devices at the operating voltage is extracted.

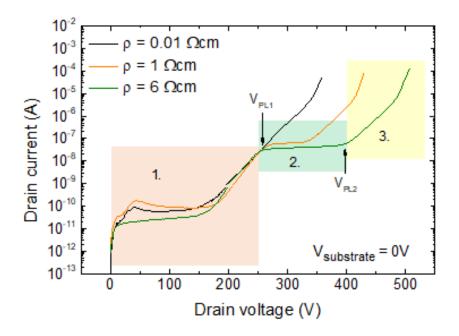

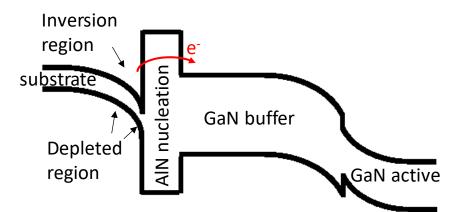

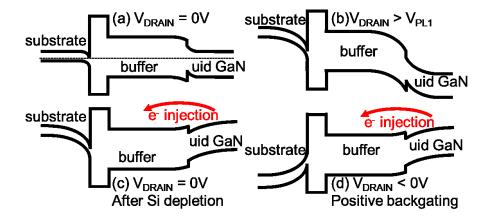

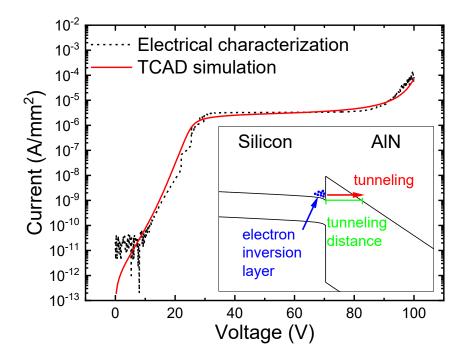

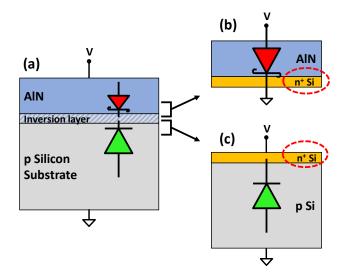

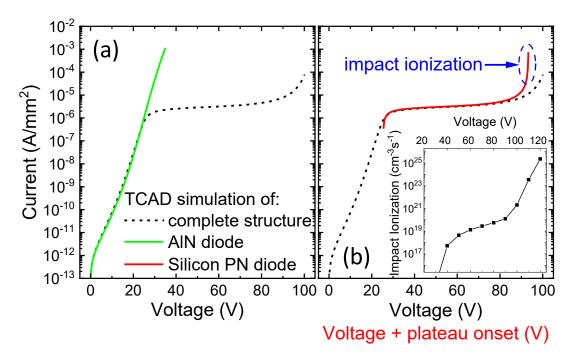

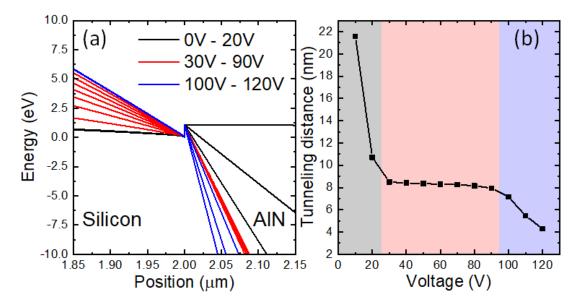

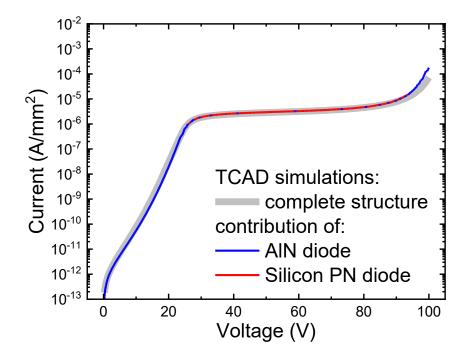

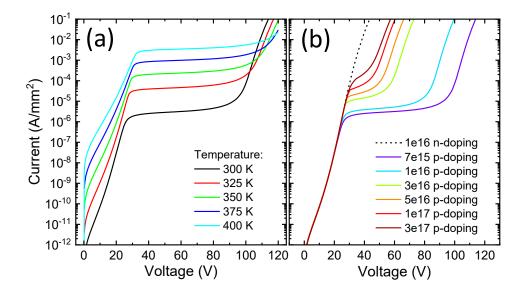

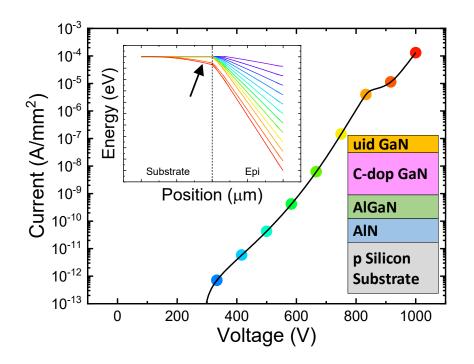

Aiming to further improve the performance of lateral High Electrons Mobility Transistors (HEMTs) in terms of vertical robustness and losses reduction, the impact of the resistivity of the silicon substrates has been evaluated. It is shown that highly resistive p-doped substrate results in a plateau region in the IV characteristic which considerably increases the vertical breakdown voltage of the devices. Nevertheless, the existence of a trade-off between the vertical robustness and the stability of the threshold voltage is demonstrated. A set of electrical characterization ascribes the threshold voltage shift to the positive backgating effect possibly related to the capacitive coupling of the partially depleted substrate which only occurs if lowly p-doped silicon is used. The origin of the plateau region is further investigated by means of a set of TCAD simulations, allowing to develop a two-diodes model which confirms the hypothesis on the substrate depletion.

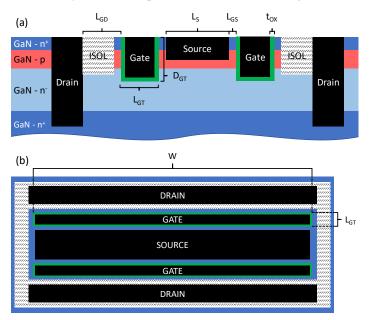

Even if stable and reliable lateral HEMTs are commercially available, their operating voltage is limited to ~ 900 V. In order to expand the applications field of the GaN-based devices to higher operating voltage, different device concepts have been developed so far. A promising solution is represented by (semi-)vertical trench gate devices, which are characterized by a thick drift layer where the OFF-state electric field spreads vertically in a bulky region, thus avoiding surface effects. Thanks to the vertical architecture, the OFF-state breakdown only depends on the thickness of the epitaxial stack, thus allowing to reach high breakdown voltages with a limited area consumption.

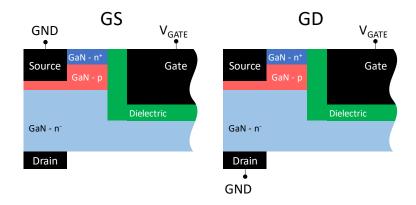

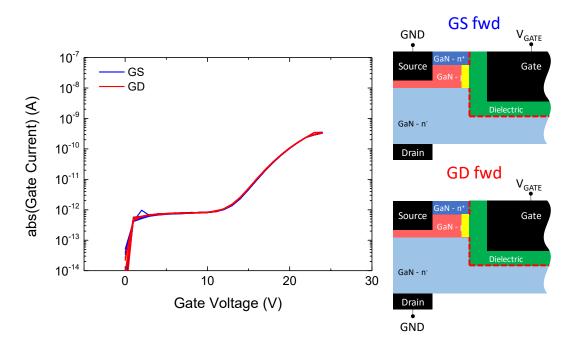

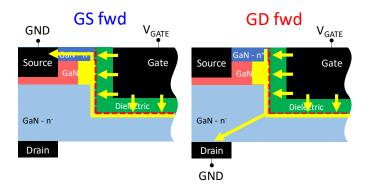

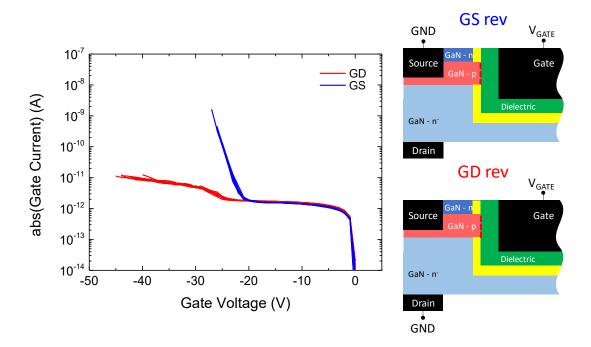

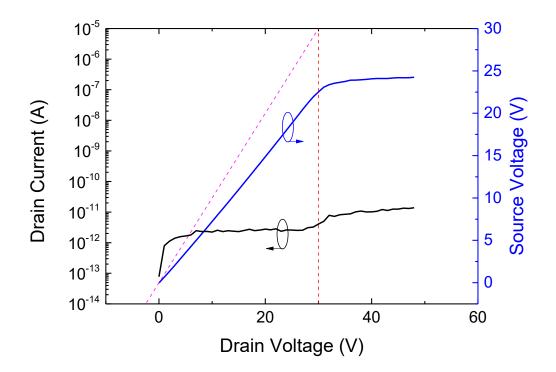

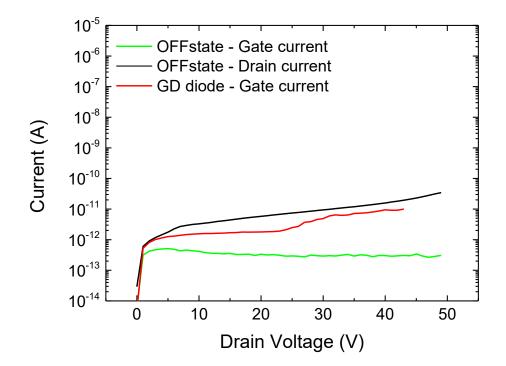

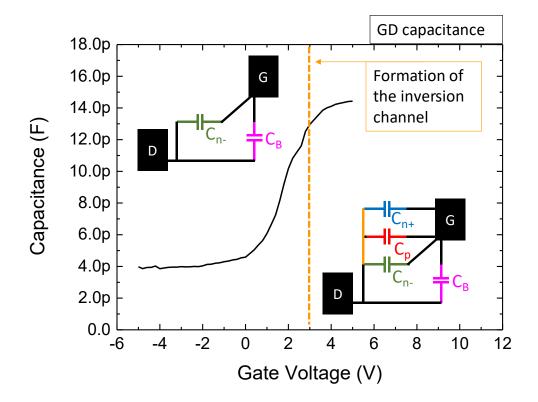

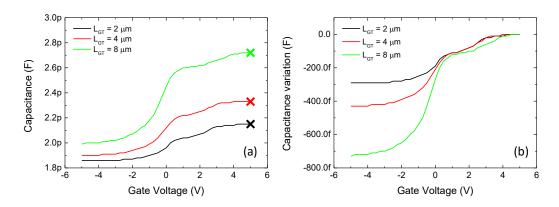

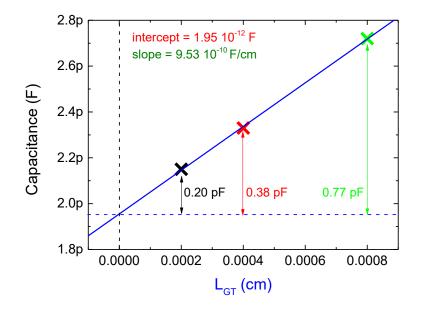

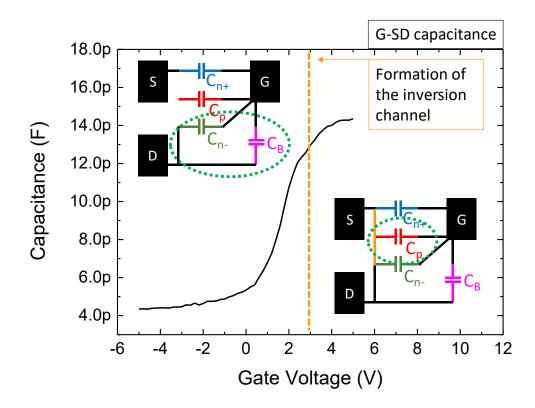

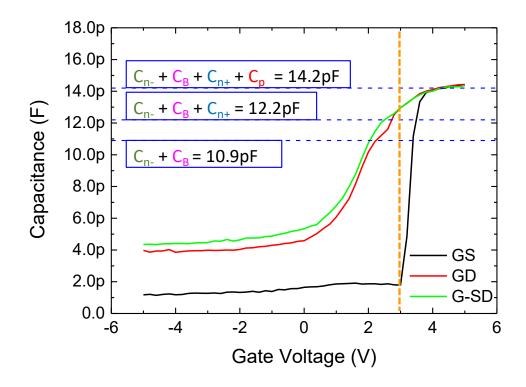

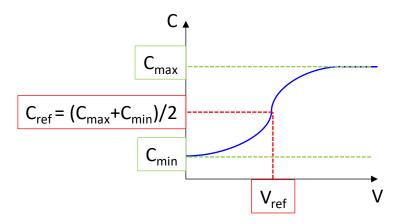

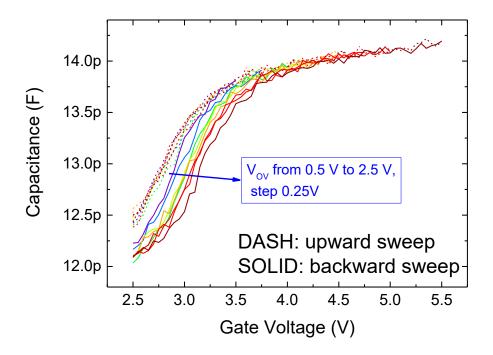

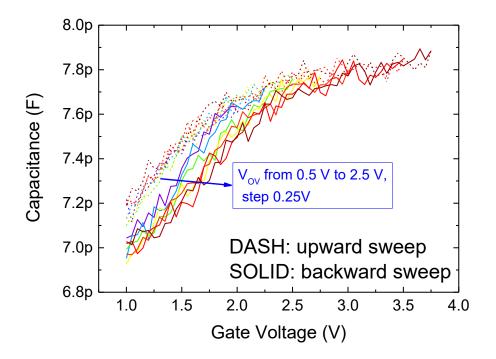

Since the carriers must flow vertically, the gate of the devices lies in an etched trench, and it consists of a Metal Oxide Semiconductor (MOS) system. Within this thesis the gate leakage is deeply studied on devices with different gate dielectric, by means of electrical characterizations performed with different connection configurations and different bias polarities. Moreover, the gate capacitance is analytically calculated, and the experimental behavior observed for the Gate-Source and Gate-Drain capacitances over the applied voltage is discussed and modeled considering the GaN bias condition close to the dielectric interface. Lastly, a preliminary dielectric trap characterization is performed by evaluating the capacitance hysteresis induced by the electric field within different gate oxide materials.

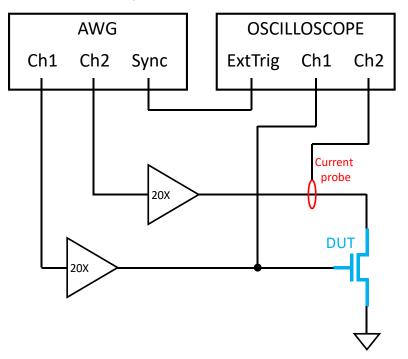

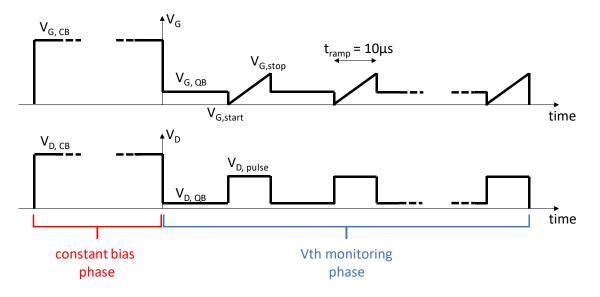

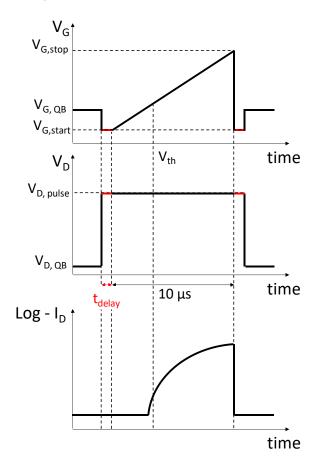

The last section of this work presents a custom setup developed for the characterization of the threshold voltage variations over the time. The stability of the threshold voltage is fundamental for allowing a device to operate properly in a switching converter. Standard pulsed systems used for the characterization of the threshold voltage allow to evaluate the impact of the bias level on the threshold variation, but no details on the time evolution can be obtained. The presented threshold transient setup monitors the threshold voltage variation over a wide time-interval, ranging from 10  $\mu$ s to 100 s, allowing the analysis of the trapping and detrapping kinetics. Moreover, by monitoring the transient variation as a function of the temperature it is possible to full characterize (energy level and cross section) the traps involved in the observed instabilities.

## Sommario

I dispositivi in GaN sono una soluzione promettente per applicazioni di potenza. Le proprietà fisiche intrinseche del nitruro di gallio consentono di migliorare notevolmente l'efficienza e di ridurre il volume della prossima generazione di circuiti switching per la conversione dell'energia.

Crescere il GaN su substrati non nativi comporta la presenza di alte densità di dislocazioni e difetti, che compromettono le performance dei dispositivi in termini di perdite ed affidabilità. Un esperimento detto "buffer decomposition experiment" ha permesso di valutare l'impatto dei diversi strati che compongono lo stack verticale di un wafer GaN-on-Silicon tramite la caratterizzazione di campioni ottenuti fermando il processo di crescita epitassiale in diversi momenti del processo. È dimostrato che sia lo spessore che la composizione dello stack verticale, oltre a migliorare la tensione di breakdown, migliora la qualità dei materiali, limitando la propagazione di dislocazioni e difetti. Inoltre, viene presentato uno studio sull'affidabilità dello strato in nitruro di alluminio (AlN) depositato su silicio; si dimostra che l'AlN si rompe per un processo percolativo, e i tempi di fallimento seguono una distribuzione di Weibull. Inoltre, viene discussa un'estesa analisi sulla affidabilità di uno stack GaN-on-Silicon, comprensiva di uno studio sistematico sulla statistica dei fallimenti. È dimostrato che il tempo di fallimento segue una distribuzione di Weibull, e, nonostante sia poco dipendente dalla temperatura, è esponenzialmente accelerato dalla tensione applicata. Infine, viene estratto il tempo di vita atteso in condizioni operative nominali.

Con l'obiettivo di migliorare ulteriormente le performance degli HEMT laterali in termini di robustezza e di riduzione delle perdite, è stato valutato il ruolo della resistività del substrato in silicio. È dimostrato che substrati di tipo p altamente resistivi causano una regione di "plateau" nella caratteristica IV del dispositivo, la quale aumenta

#### Sommario

considerevolmente la tensione di breakdown del dispositivo. Nonostante questo, è stato evidenziato un trade-off tra la robustezza dello stack verticale e la stabilità della tensione di soglia. L'origine fisica della regione di plateau è stata inoltre investigata tramite simulazioni TCAD, che hanno permesso di sviluppare un modello a due diodi.

Nonostante siano disponibili nel mercato dispostivi laterali stabili e affidabili, la loro tensione nominale non supera i 900V. Nei dispositivi con architettura verticale, il breakdown in off-state dipende solo dallo spessore dello stack epitassiale, consentendo di raggiungere alte tensioni di fallimento con un consumo di area limitato. In questa tesi la corrente di leakage di gate viene dettagliatamente studiata in dispositivi verticali con diversi dielettrici di gate, tramite caratterizzazioni effettuate con diverse configurazioni di connessioni e diverse polarità. Inoltre, la capacità di gate è calcolata analiticamente, e l'andamento sperimentale osservato per le capacità Gate-Source e Gate-Drain al variare della tensione di gate sono analizzate e modellizzate considerando il potenziale del GaN vicino all'interfaccia con il dielettrico.

Nell'ultima parte della tesi viene presentato un setup custom sviluppato per caratterizzare le variazioni della tensione di soglia nel tempo. La stabilità della soglia è fondamentale per assicurare che il dispositivo funzioni correttamente in un convertitore switching. I sistemi impulsati convenzionali utilizzati per la caratterizzazione della soglia permettono di valutare l'effetto del bias sulle variazioni della soglia, ma non danno nessuna informazione sull'evoluzione temporale. Il setup presentato monitora le variazioni della tensione di soglia in un intervallo temporale ampio, che spazia dai 10 µs ai 100 s, consentendo di analizzare le cinetiche di intrappolamento e detrappolamento. Inoltre, monitorando i transienti di soglia in funzione della temperatura si possono caratterizzare (energia e sezione di cattura) le trappole che causano le instabilità osservate.

## Introduction

The electrical energy is nowadays extensively used around the word, and it is expected to be the most widespread form of energy by 2040. Eco-friendly and highefficiency systems are helping us to reduce energy wasting; nevertheless, the digital society that is developing will required within few years new power-consuming services (communications, digital services, data storage, logistics, transport...). This progression is pushing the market to develop advanced systems for the production, the distribution, the storage and the conversion of the electrical energy.

The electrical energy is always stored or delivered in a different form with respect what needed by the final device. For example, the electrical grid provide an AC voltage, while most of electronic appliance (TV, PC, smartphone, LED laps...) require a relatively low DC voltage; another example is the electric cars, in which the energy is stored in high voltage DC batteries, and it needs to be converted into AC power to be supplied to the AC motors; a third case is the DC output of the photovoltaic systems, which must be converted into AC voltage to be released into the high voltage electrical grid. All these electrical conversions are assigned to complex switching electronic circuits (DC-DC converters, inverters...) which needs to be as more efficient as possible, to minimize the power losses and the wasting of energy.

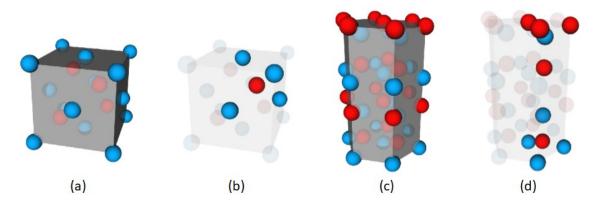

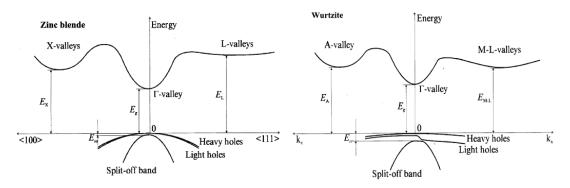

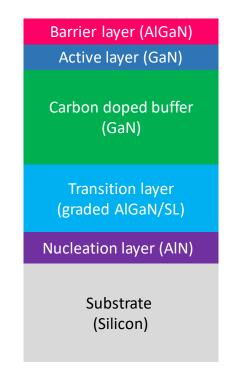

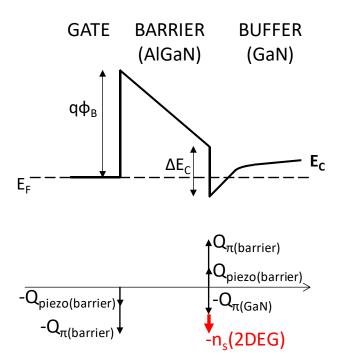

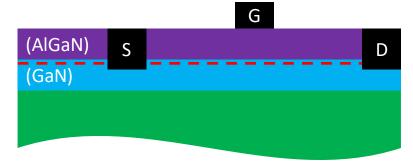

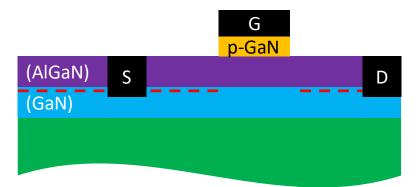

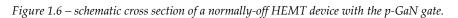

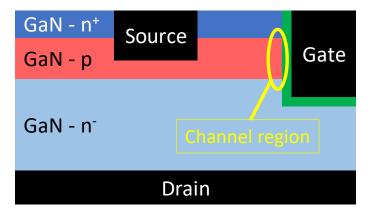

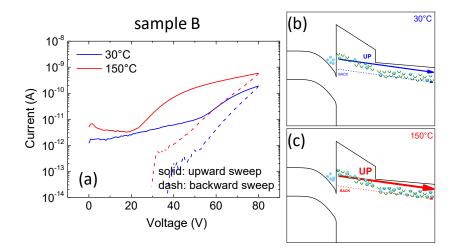

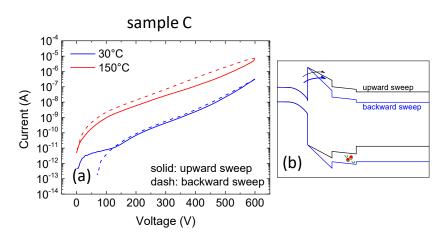

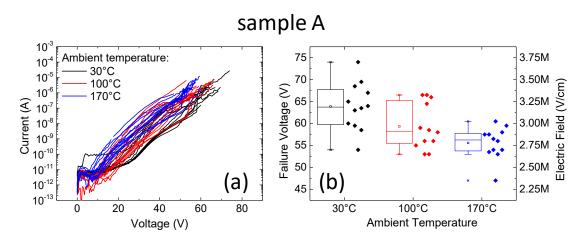

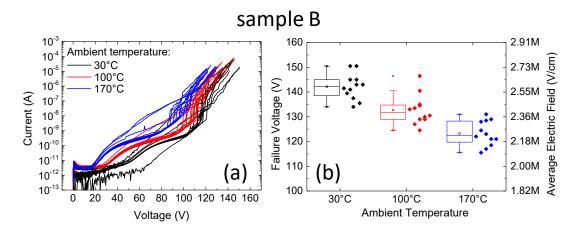

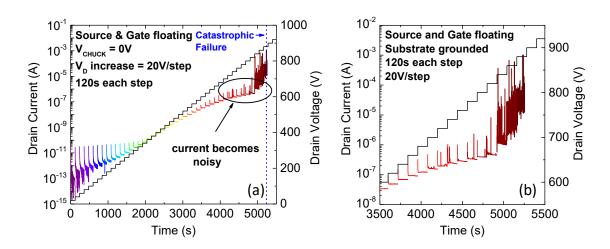

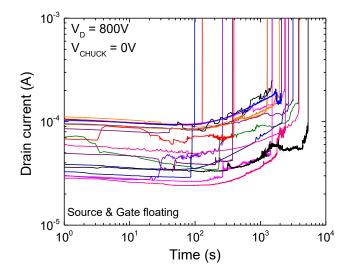

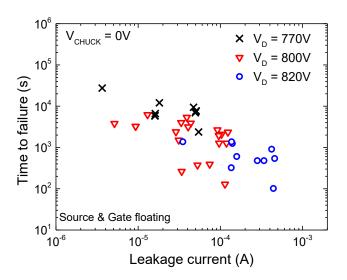

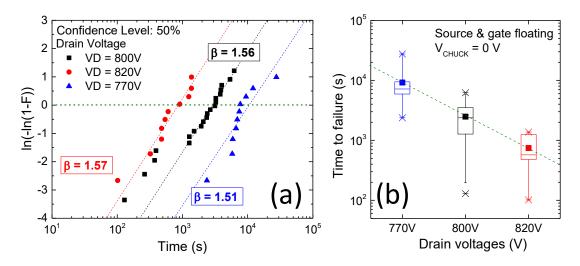

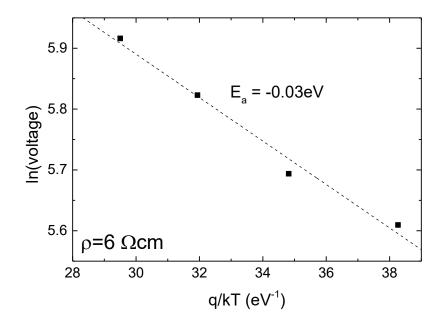

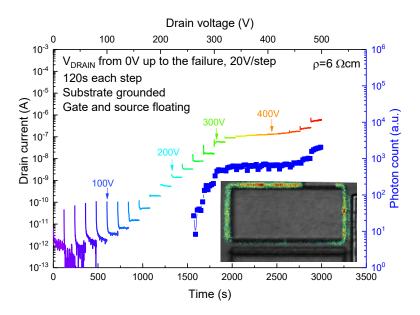

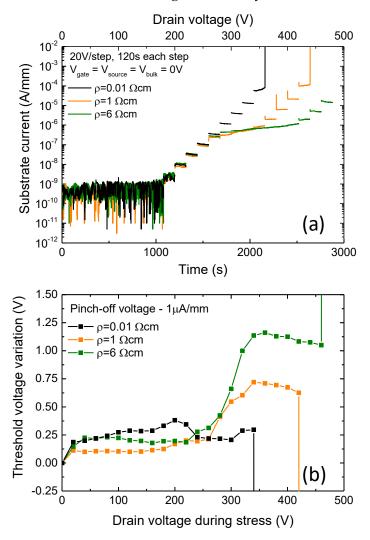

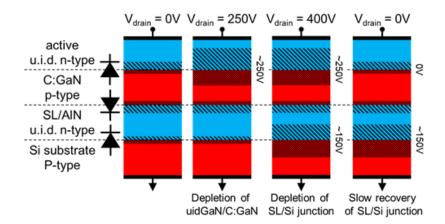

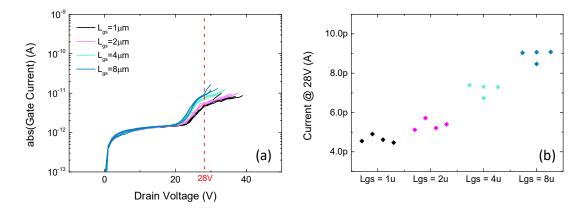

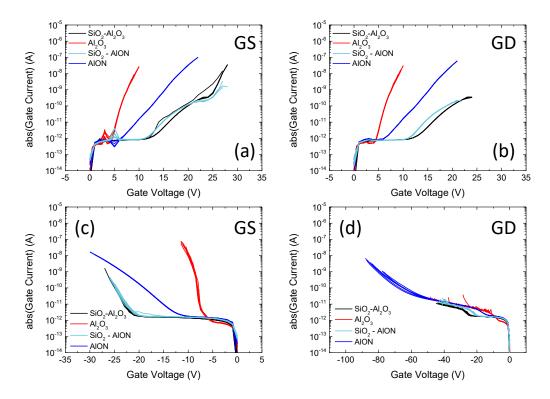

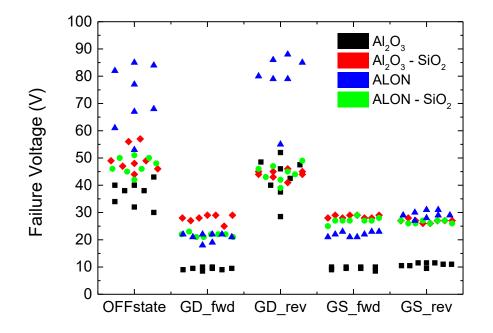

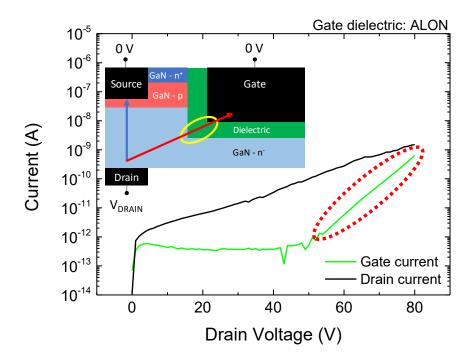

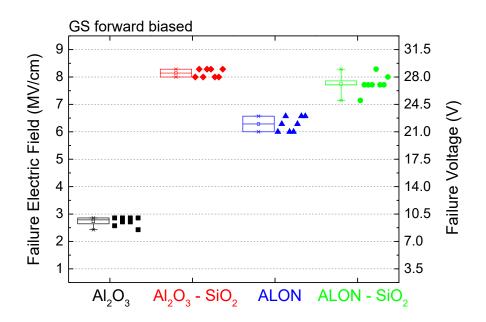

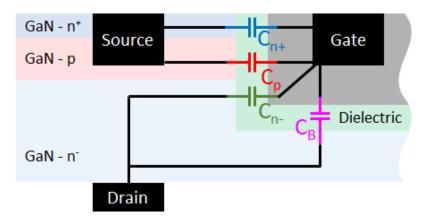

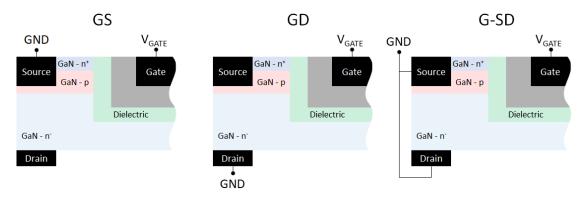

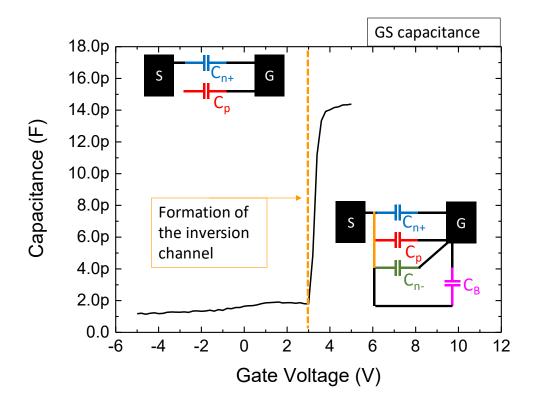

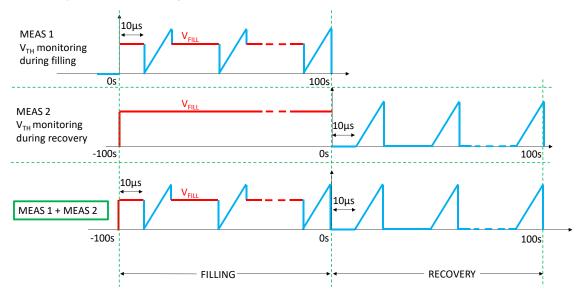

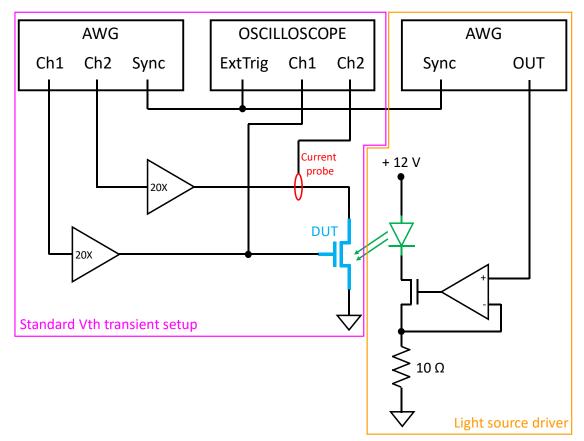

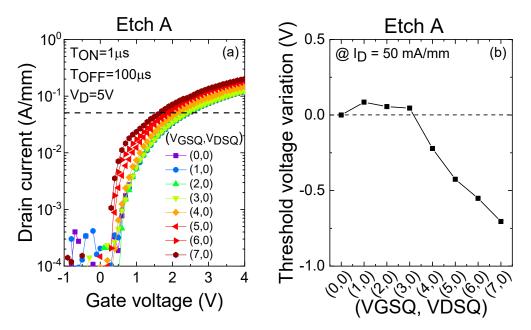

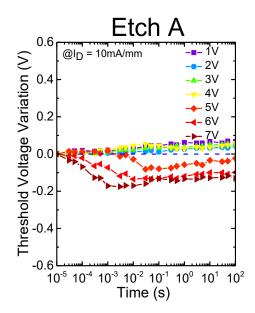

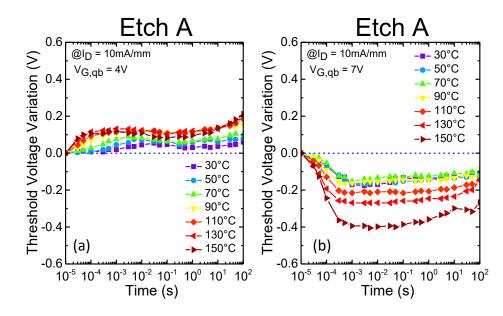

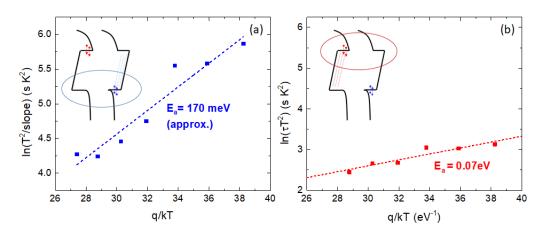

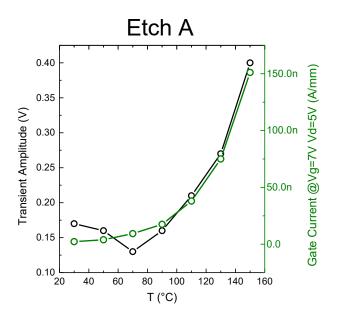

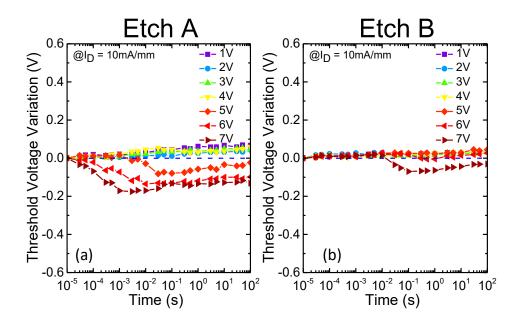

The active component of these switching converters is a transistor that, driven by a controller, operates like a switch. This latter during the operation go from on OFF-state condition, in which it must block a high voltage with very low current losses, to an ONstate condition, where the current that flows into the devices should give a negligible voltage drop, minimizing the resistive losses. Silicon-based devices are approaching the theoretical limits of the semiconductor material, and no significant improvements can be obtained. In order to improve the efficiency of the new-generation conversion systems and to fit the market demand, new devices based on novel materials have been developed over the last years.