# Nonlinearities of Multi-Sampled Phase-Shifted PWM in Unbalanced Multi-Cell Converters

Ruzica Cvetanovic, *Student Member, IEEE*, Ivan Z. Petric, *Member, IEEE*, Paolo Mattavelli, *Fellow, IEEE*, Simone Buso, *Member, IEEE*

Abstract—This article reveals, analyzes and proposes the method to mitigate nonlinear effects of multi-sampled multiupdate (MSMU) digital phase-shifted pulsewidth modulators (PS-DPWM) that appear in unbalanced multi-cell voltage-source converters (MC-VSCs). For balanced MC-VSCs, the harmonic cancellation of PS-DPWM allows for an increase in the sampling frequency, ensuring that the average current is acquired at the peaks, valleys, and intersections of all triangular carriers. For unbalanced operation, which is typically encountered in practice, e.g., due to cell voltage mismatch in multilevel MC-VSCs and inductance mismatch in interleaved MC-VSCs, harmonic cancellation of PS-DPWM is compromised and, thus, the increased sampling frequency brings switching ripple in the feedback signal. Since in MSMU control the modulating signal is also updated at peaks, valleys, and intersections of all carriers, this may cause vertical intersections between the modulating signal and the carriers, resulting in specific nonlinear effects. The nonlinearities are shown to introduce limit-cycle oscillations and output waveform distortion. A method to prevent such detrimental impact of MSMU-PS-PWM is also proposed. A simple analytical procedure is proposed to quantify the analyzed non-linear effects, revealing that they are more emphasized for higher levels of imbalance and control bandwidth. Moreover, the modulator nonlinearity is shown to decrease as the number of cells increases. The analyses are verified in simulations and experiments, using laboratory prototypes of three- and four-level MC-VSCs.

Index Terms—Interleaved, multilevel, phase-shifted pulsewidth modulation, multi-cell converters, multi-sampled multi-update control, limit-cycle oscillations

# I. INTRODUCTION

OWADAYS, multi-cell voltage source converters (MC-VSCs) are widely used not only to overcome the voltage and current constraints of single power switches, but also to achieve ultra-high efficiency, power density, and dynamic performance [1]–[7]. Cells within MC-VSCs can be stacked

Manuscript received May 17, 2023; revised September 15, 2023; accepted November 05, 2023. The research has been funded by the project "Network 4 Energy Sustainable Transition – NEST" under the National Recovery and Resilience Plan (NRRP), Mission 4 Component 2 Investment 1.3 - Call for tender N. 341 del 15.03.2022 of Ministero dell'Università e della Ricerca (MUR), funded by the European Union – NextGenerationEU. The NEST project code is PE0000021, Concession Decree No. 1561 of 11.10.2022 by MUR, CUP C93C22005230007.

- R. Cvetanovic, and S. Buso are with the Department of Information Engineering, University of Padova, 35131 Padova, Italy (e-mail: ruz-ica.cvetanovic@phd.unipd.it; simone.buso@dei.unipd.it).

- I. Z. Petric is with Hanwha Q CELLS America Inc., Santa Clara, California, USA (e-mail: ivan.petric@phd.unipd.it).

- P. Mattavelli is with the Department of Management and Engineering, University of Padova, 36100 Vicenza, Italy (e-mail: paolo.mattavelli@unipd.it).

in series or in parallel, resulting in multilevel [2]–[6] or interleaved MC-VSCs [7]–[9].

A widely used modulation strategy for MC-VSCs is the digital phase-shifted pulsewidth modulation (PS-DPWM) [2]–[5], [7], where the carriers of the subsequent cells are phase-shifted with respect to each other, so that harmonic cancellation is achieved at the output [10], [11]. Under balanced conditions, this yields an increased frequency of the output current ripple, i.e., frequency multiplication [12], enabling output filter reduction [7], [12] and control loop bandwidth improvement [6], [13]–[17].

For regulating the output current of PS-DPWM MC-VSCs, multi-sampled multi-update (MSMU) control is a widely adopted strategy, due to improved dynamic performance and robustness, offered by a significant reduction of the modulation delay [13]-[16], [18]-[21]. In MSMU-PS-DPWM, the sampling of the output current and update of the modulating signal are performed at peaks, valleys, and intersections of all triangular carriers. Due to the frequency multiplication of PS-DPWM, MSMU control in balanced MC-VSCs without any non-idealities does not feature any switching ripple component of the modulating signal. Therefore, MSMU in MC-VSCs is often claimed to be a natural linear extension of the doublesampled double-update control used in two-level VSCs [13], [14], [16], [21], completely neglecting thereby its behavior in unbalanced scenarios, which are the most often encountered in practice [1], [9], [22]–[25].

Since in MSMU the modulating signal is updated at the peaks, valleys, and intersections of all carriers, vertical intersections between the modulating signal and the carriers may occur around certain operating points [19], [26], [27]. In MSMU two-level VSCs, vertical intersections occur even in steady-state conditions as the switching ripple is always introduced into the feedback loop. On the other hand, in balanced MSMU MC-VSCs, vertical intersections are not possible in steady-state conditions. Nevertheless, ideally balanced operation is rarely achieved in practice due to tolerances of passive components, timing mismatches in gatedriving circuits, transients, different nature of the sources/loads connected to each cell's dc link, etc. [1], [5], [9], [22]-[25], [28]–[32]. Imbalance deteriorates frequency multiplication and causes the switching ripple to appear in the feedback. This may also happen under balanced conditions, if center-pulse (synchronous) sampling [33] is impaired, e.g., due to delays in driver circuits, dead-times, delays in sensing circuits, etc. As a consequence, in its sampled variant, the modulating signal features jump discontinuities [27], which pose a risk for vertical intersections. Though their impact in two-level VSCs with MSMU-DPWM is well investigated [27], the behavior of MSMU-PS-DPWM in unbalanced MC-VSCs has not been addressed in the literature so far.

To fill in the gaps of previous research, this paper analyses the discontinuity-related nonlinear effects of MSMU-PS-DPWM that appear in unbalanced MC-VSCs. For accurate modeling of PS-DPWM behavior, a static transcharacteristic is defined for each phase-shifted carrier separately. Then, it is shown that, similarly to MSMU two-level VSCs, depending on the sign of the modulating signal discontinuity, vertical intersections cause reduced-gain, zero-gain, and infinite-gain (jitter) zones in the transcharacteristics [26], [27], [34]. In contrast to MSMU two-level VSCs, it is demonstrated that vertical intersections in MSMU MC-VSCs always cause limit-cycle oscillations (LCOs). For MC-VSCs with a dc operating point, this prevents steady-state operation to be achieved, whereas in case of ac operating point, the output current is strongly distorted. Thus, in industrial applications where a certain degree of imbalance is most-often encountered, a widely used MSMU-PS-DPWM may bring a detrimental impact, which is for the first time analyzed in this article and demonstrated using laboratory prototypes of three- and four-level MC-VSCs. The extent of discontinuity-related nonlinear effects in unbalanced MC-VSCs with MSMU-PS-DPWM is shown to be proportional to the relative imbalance magnitude and relative crossover frequency of the current control loop. As the number of cells increases, the modulating waveform discontinuities are reduced, causing therefore nonlinearity of MSMU-PS-DPWM to diminish. Still, to prevent the detrimental impact of modulator non-linearity that is pronounced in unbalanced multi-level and interleaved converters with lower number of cells, some provision has to be taken in practical applications. As one such a method, this article proposes digital feedback filtering which removes the switching ripple from the sampled current without impairing control loop's small-signal dynamic performance. Although reported before for two-level VSCs with MSMU-DPWM [35], [36], use of ripple removal filters in MC-VSCs with MSMU-PS-DPWM have not been considered before, as ripple-induced nonlinearities were neglected.

This article is organized as follows. In Section II, MSMU-PS-DPWM control of MC-VSCs is introduced, and the basic types of intersections between the modulating signal and the carriers are outlined, along with an explanation of the jittering mechanism. The impact of mismatched dc link voltages in multilevel MC-VSCs and mismatched inductances in interleaved MC-VSCs on the appearance of the switching ripple component in the modulating signal is illustrated in Section III. The resulting nonlinear effects are quantitatively analyzed in Section IV and their adverse effect on converter's input and output waveforms is illustrated. In Section V, experimental measurements of modulator transcharacteristics are shown to be in excellent agreement with simulations and analytics. The detrimental impact of limit-cycle oscillations on the performance of dc-dc and dc-ac MC-VSCs is also experimentally verified illustrated in Section V in time domain. Section VI concludes the article. As an addendum, suppression of the reported non-linear effects of MSMU-PS-DPWM is addressed

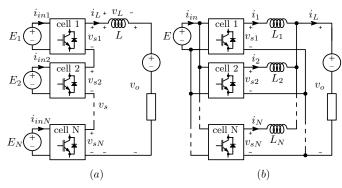

Fig. 1: Single-phase MC-VSC: (a) multilevel; (b) interleaved topology. Each cell can be realized as a half- or full-bridge.

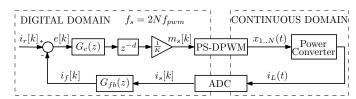

Fig. 2: System block diagram of digital, current-controlled, single-phase, MC-VSC with symmetric MSMU-PS-DPWM.

in Appendix.

# II. MULTI-SAMPLED MULTI-UPDATE CONTROL OF MULTI-CELL CONVERTERS

#### A. System Description

In this article, digital current-controlled MC-VSCs with MSMU-PS-DPWM are considered. As examples of multilevel and interleaved MC-VSCs, single-phase converters consisting of N series- and parallel-stacked half-bridge or full-bridge cells, shown in Fig. 1, are used. Nevertheless, the presented methodology can be applied to other single- or multi-phase multi-cell topologies with MSMU-PS-DPWM.

In Fig. 1a, each cell is supplied from a separate dc source,  $E_i$ . The output voltages of all cells,  $v_{s1}...v_{sN}$ , are summed to form the output voltage of the MC-VSC,  $v_s$ . The difference between  $v_s$  and load voltage  $v_o$  is applied to an inductive filter, L. In Fig. 1b, all cells are supplied from the same dc source, E. The output voltage of each cell,  $v_{si}$ , is applied to an inductor,  $L_i$ , and the currents of all the inductors,  $i_1...i_N$ , are summed to form the output current,  $i_L$ , of the MC-VSC.

A block diagram of the considered current-controlled system is shown in Fig. 2. An analog-to-digital converter (ADC) performs the transition from continuous to digital domain. The sampling of  $i_L$  is performed at the center of the applied voltage pulses, ensuring the center-pulse (synchronous) sampling [33], with the rate  $f_s$  equal to the total number of edges that can be modulated. Under balanced conditions this ensures removal of the switching ripple from  $i_L$ . Assuming half-bridge cells and PS-DPWM with  $\frac{360^\circ}{N}$  phase-shift<sup>1</sup> between the adjacent trian-

$<sup>^{1}</sup>$ As a starting point, this article considers PS-DPWM with a fixed phase-shift value (equal to  $\frac{360^{\circ}}{N}$ ), leaving the consideration of PS-DPWM with variable phase-shift [23], [28]–[32] for future studies.

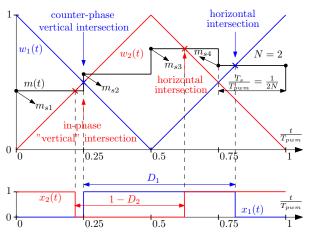

Fig. 3: Different intersections between m and  $w_i$  for MSMU-PS-DPWM with N=2. For DPWM<sub>1</sub>, corresponding to  $w_1$ , a counter-phase vertical and a horizontal intersection occur during negative and positive slope of  $w_1$ , respectively. For DPWM<sub>2</sub>, corresponding to  $w_2$ , an in-phase "vertical" and a horizontal intersection occur during positive and negative slope of  $w_2$ , respectively. To prevent multiple commutations, the switching action of DPWM<sub>i</sub> is defined by the first intersection between m and  $w_i$ , which turns in-phase "vertical" into horizontal intersections.

gular<sup>2</sup> carriers [10], this yields  $f_s = 2Nf_{pwm} = N_{ms}f_{pwm}$ , where  $f_{pwm}$  is the switching (carrier) frequency and  $N_{ms}$  is the multi-sampling factor. In the case of full-bridge cells with bipolar PS-DPWM, nothing changes compared to half-bridge cells. The analysis is also easily extendable to unipolar PS-DPWM.

If the application of interest requires digital feedback filtering, the sampled current  $i_s$  can be processed by  $G_{fb}(z)$ , resulting in  $i_f$ <sup>3</sup>. By subtracting  $i_f$  from the reference  $i_r$ , the error signal e is obtained and used as the input to the current controller  $G_c$ . The controller output update is delayed by d sampling periods  $T_s = \frac{1}{f_s}$ , due to the finite execution time [33]. The voltage reference generated by the current controller is scaled by K to the range [0,1], resulting in the digital modulating signal  $m_s$ . For half-bridge cells  $K = E_{\Sigma}$ , where  $E_{\Sigma} = NE_n$  for multilevel and  $E_{\Sigma} = E_n$  for interleaved converters, and  $E_n$  is the cell's nominal input dc voltage. For full-bridge cells  $K = 2E_{\Sigma}$ , and an additional offset has to be added, which is not shown in Fig. 2 as it does not affect the proposed analysis. The entire digital system runs at the rate determined by the sampling frequency  $f_s$ .

The PS-DPWM serves as an interface between digital and continuous domains. This article considers symmetric PS-DPWM, where the same signal  $m_s$  is used to modulate each cell. Its inherent ZOH function transforms  $m_s$  to m and compares it with the carrier  $w_i$ , belonging to DPWM<sub>i</sub>. In this

<sup>2</sup>PS-DPWM with triangular carriers simplifies the choice of sampling instants that coincide with the average current values [5]. Moreover, it allows dual-edge modulation [37], which improves the transient response capabilities; hence, triangular carriers are typically chosen over the sawtooth ones. For this reason, the following analysis considers the triangular carriers.

<sup>3</sup>Motivation for digital feedback filtering can be various, e.g. to enhance noise suppression capabilities [17], [38], [39] or to avoid introducing switching ripple in feedback under unbalanced operation, as discussed in Appendix. Other than the analyses in Appendix, MSMU-PS-DPWM control system without digital feedback filtering ( $G_{fb}=1$ ) is considered in this article, in order to provide a generic analysis of the underlying phenomena.

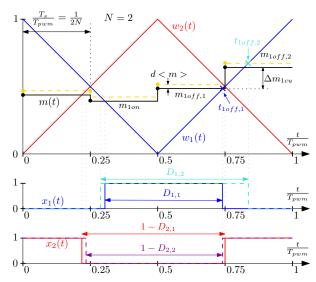

Fig. 4: Example of an operating regime that may cause jitter amplification for MSMU-PS-DPWM with N=2. In-phase operation that is present for  $w_1$ , together with the modulating signal discontinuity, poses a risk for limit cycling (duty cycle jittering).

way, the switching signal  $x_i$  is obtained, which is a square waveform with duty cycle  $D_i^4$ . It is used to control the power switches within the *i*-th cell of the MC-VSC.

# B. Intersections Between Modulating Signal and Carriers

In multi-sampled single- and double-update PS-DPWM, the modulating signal for each cell is updated at the peaks or/and valleys of the carrier corresponding to that cell [16], [18]. This results in only horizontal intersections between the modulating signal and the carrier. In MSMU-PS-DPWM, the modulating signal, which is the same for all cells, is updated at every sampling instant, i.e., at the peaks, valleys and intersections of all carriers, which is more than twice per carrier period,  $T_{pwm} = \frac{1}{f_{pwm}}$ . Thus, due to the discontinuity of m, vertical intersections between m and  $w_i$  are now possible [19], [20], [27].

Due to the imposed synchronization between the update of m and the carriers, vertical intersections may occur only around certain operating points, that are determined by  $N_{ms}$  [27]. These operating points are defined as the *critical* dutycycles

$$D_c = \frac{2k}{N_{\text{max}}} = \frac{k}{N} \tag{1}$$

where  $1 \le k < N$  and k is an integer.

To analyze the modulator nonlinearities induced by vertical intersections, it is important to differentiate between inphase and counter-phase operation, determined by the relation between the slope of m and the slope of  $w_i$  [27]. When, at the update instant closest to the intersection with  $w_i$ , the slope of m has the same sign as the slope of  $w_i$ , the intersection and the operation of DPWM $_i$  are referred to as in-phase [27]. On the other hand, when the slopes have

<sup>4</sup>In the steady-state without any non-idealities ( $m_s=D=const.$ ), due to symmetric PS-DPWM,  $D_1=D_2=...=D_N=D$  and  $V_o=DE_{\Sigma}$ , where  $V_o$  is the (dc) steady-state value of the load voltage  $v_o$ .

opposite signs, the intersection and the operation of DPW $M_i$  are referred to as *counter-phase* [27]. An interesting property of MSMU-PS-DPWM is that an in-phase operation for one carrier is a counter-phase operation for another carrier, which is illustrated in Fig. 3 for MSMU-PS-DPWM with N=2 (to make the illustration clear, but the same holds also for higher N). This is because the modulating signal is updated at instants when exactly two carriers intersect. As shown in the following sections, this has a detrimental impact on the nonlinear phenomena that appear in MC-VSCs.

#### C. Jitter Amplification Phenomenon

In [27], [34] it is shown that for two-level converters inphase operation and the modulating signal discontinuity result in jitter amplification phenomenon. Since in case of MC-VSCs, as previously explained, at least one of the phase-shifted carriers always features in-phase operation, vertical intersections always result in jitter amplification phenomenon, which is for the first time analyzed in this article. The mechanism behind it is illustrated in Fig. 4 and briefly explained below, using MSMU-PS-DPWM with N=2 as an example, but the conclusions remain the same also for other values of  $N^5$ .

In the example shown in Fig. 4, an in-phase operation is present for  $w_1$ . Consider an initial operating point, where the falling edge of  $x_1$  is determined by the intersection between  $w_1$  and the modulating segment  $m_{1off,1}$ , resulting in the duty cycle  $D_{1,1}$ . In case the closed-loop control yields a small change of the controller's output, such that a higher duty cycle is required, the modulating signal is incremented by a certain amount d < m >. As illustrated in Fig. 4, a very small positive d < m > causes the falling edge of  $x_1$  to be determined by the following segment  $m_{1off,2}$ , which changes the duty cycle from  $D_{1,1}$  to  $D_{1,2}$ . As the applied duty cycle is higher than the required one, the controller will respond by decreasing the value of m, which, in the subsequent switching period, may again cause the segment  $m_{1off,1}$  to intersect with  $w_1$ . Thus,  $x_1$ is determined by the modulating signal discontinuity  $\Delta m_{1cu}$ , rather than d < m >. This results in limit cycling (duty cycle jittering) that has detrimental impact on system performance, as illustrated by time domain waveforms from simulations (Fig. 14 and Fig. 21 (b)) and experiments (Fig. 19 and Fig. 20 (a)-(b)) for MC-VSCs with dc and ac operating point. The incapability of MSMU-PS-DPWM to achieve desired duty cycle is manifested as "increased-gain" regions in the modulator static transcharacteristics corresponding to the carriers that feature an in-phase operation, as explained in Section IV.A.

# D. Enabling Mechanism Behind Vertical Intersections

In order for vertical intersections to occur, some disturbance is required when the operating point is close to  $D_c$ . For example, a change of m can be caused by reacting to transient variations or, under steady-state conditions, by the switching ripple component. In this article, the effects due to the latter are addressed.

$^5$ For high enough N, i.e.,  $N_{ms}$ , discontinuity of the modulating signal is almost completely removed, eliminating thereby non-linear effects caused by it and making the MSMU-PS-DPWM feature analog-like performance.

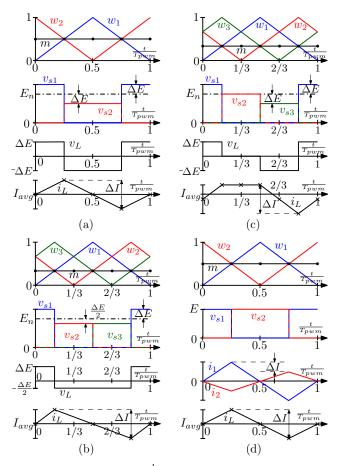

Fig. 5: Switching ripple at  $D_c = \frac{1}{N}$  in multilevel MC-VSC with: (a) N=2, imbalance (3); (b) N=3, imbalance (3); (c) N=3, imbalance (4); and (d) unbalanced interleaved MC-VSC with N=2 and  $L_1 < L_2$ .

For balanced MC-VSCs with MSMU-PS-DPWM, the ripple frequency is increased to  $Nf_{pwm}$ , which allows for sampling the average current with the rate  $f_s=2Nf_{pwm}$ . Therefore, considering the ideal choice of sampling instants, switching ripple of  $i_L$  is not introduced in the feedback signal and m does not contain any switching ripple component. However, with imbalance, the frequency multiplication is lost and the switching ripple appears in m.

Mismatched values of the cells' dc link voltages, in case of multilevel MC-VSCs, and of the inductances, in case of interleaved MC-VSCs, are used in this article as illustrative examples of the imbalance. In order to analyze the nonlinearity of MSMU-PS-DPWM with such an imbalance, it is of interest to gain insight into the shape of the switching ripple waveform at  $D_c$ , as addressed in the next section.

# III. SWITCHING RIPPLE AROUND CRITICAL OPERATING POINTS IN UNBALANCED MULTI-CELL CONVERTERS

# A. Output Current Ripple in Multilevel MC-VSCs with Mismatched DC Links

The current ripple waveform in unbalanced multilevel MC-VSCs, depends, in a general case, on the dc link voltages of all the cells. Thus, general statements about its shape require complicated spectral analyses [10], [40], which lack a clear insight, especially for higher N. In order to illustrate core

principles without using complex mathematical procedures, for the subsequent analyses, we introduce some assumptions regarding the distribution of imbalance among the cells. Nevertheless, it is important to emphasize that, as verified in simulations and experiments, the resulting nonlinear effects only quantitatively change in the most general case with an arbitrary imbalance distribution.

At first, it is assumed that  $\sum_{i=1}^{N} E_i = NE_n$ . For N=2, this yields two possible imbalance distributions:  $E_1 = E_n + \Delta E$ ,  $E_2 = E_n - \Delta E$ , and  $E_1 = E_n - \Delta E$ ,  $E_2 = E_n + \Delta E$ , where  $\Delta E > 0$  is referred to as the magnitude of the voltage imbalance. As an example, waveforms of interest at  $D_c = \frac{1}{2}$  are shown in Fig. 5a, for a multilevel MC-VSC with two half-bridge cells,  $E_1 = E_n + \Delta E$  and  $E_2 = E_n - \Delta E$ . As seen, the output current ripple at  $D_c = \frac{1}{2}$  is triangular with the fundamental frequency component at  $f_{pwm}$  and the peak-peak value

$$\Delta I = \frac{k_{D_c} \Delta E}{f_{pwm} L} = \frac{\Delta E_{D_c}}{f_{pwm} L} \tag{2}$$

where  $k_{D_c} = \frac{N}{N-1}D_c(1-D_c)$ . There are cases, also for N>2, where the output current ripple at  $D_c$  is a triangular waveform with the fundamental frequency component at  $f_{pwm}$  and the peak-peak value defined by (2). One such example is the following distribution of imbalance

$$E_1 = E_n + \Delta E, E_2 = \dots = E_N = E_n - \frac{\Delta E}{N - 1}.$$

(3)

Relevant waveforms with such imbalance for a multilevel MC-VSC with three half-bridge cells are shown in Fig. 5b, at  $D_c=\frac{1}{3}$ . It is easy to show that for some imbalance distributions, the ripple is not triangular. For example, in Fig. 5c an illustration is given for

$$E_1 = E_n + \Delta E, E_2 = E_n, E_3 = E_n - \Delta E.$$

(4)

Nonetheless, it can be shown that for an arbitrary imbalance distribution, the peak-peak value of the current ripple at  $D_c$ ,  $\Delta I$ , is proportional to the joined imbalance magnitude,  $\Delta E_{D_c}$ , determined at each  $D_c$  as described below. Namely, due to PS-DPWM, the voltage across the inductor,  $v_L(t)$ , is a piecewise constant waveform, which, in a general case, at  $D_c$  features N different values  $V_{Lh}$  within one  $T_{pwm}$ , where h=(1,...,N) denotes the index of the segment, starting from  $w_1=0$ , during which  $v_L(t)=V_{Lh}$ . Each  $V_{Lh}$  causes  $i_L$  to change for  $\Delta I_h$  within the time period  $\frac{T_{pwm}}{N}$ , i.e.,  $\Delta I_h=\frac{V_{Lh}}{Nf_{pwm}L}$ . By finding the array of subsequent voltages applied to the inductor that features the highest sum  $\Sigma$ , the peak-peak value of the inductor current ripple at  $D_c$ , in case of an arbitrary imbalance distribution, is determined

$$\Delta I = \frac{\Sigma}{N f_{pwm} L} = \frac{\Delta E_{Dc}}{f_{pwm} L}.$$

(5)

Note that for balanced operation where  $\Delta E_{D_c} = 0$ , at  $D_c$   $\Delta I = 0$ , which is a known property of PS-DPWM. Due to this property, the operating points defined by (1) are sometimes called nominal conversion ratios [5].

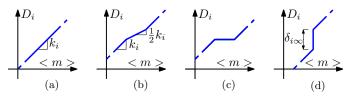

Fig. 6: Types of zones that may appear in transcharacteristic of  $DPWM_i$ : (a) Linear behavior obtained with double horizontal intersections; (b) Reducedgain zone obtained with a single counter-phase vertical intersection; (c) Zero-gain (dead-band) zone obtained with double counter-phase vertical intersections; (d) Infinite-gain (jitter) zone obtained with in-phase "vertical" intersection.

# B. Output Current Ripple in Interleaved MC-VSCs with Mismatched Inductances

In order to illustrate influence of mismatched inductances on the shape of the output current ripple at  $D_c$  in interleaved MC-VSCs, the waveforms of interest are shown in Fig. 5d for an interleaved MC-VSC with two half-bridge cells,  $L_1 = L_n - \Delta L$  and  $L_2 = L_n + \Delta L$ , where  $L_n$  is the nominal inductance and  $\Delta L > 0$  is the magnitude of the inductance imbalance. As seen from Fig. 5d, the current ripple exhibits the same waveform as the one in Fig. 5a, with the peak-peak value given by

$$\Delta I = \frac{D_c E}{f_{pwm}} \left( \frac{1}{L_n - \Delta L} - \frac{1}{L_n + \Delta L} \right). \tag{6}$$

It can be shown that, also in interleaved MC-VSCs with N>2, the influence of the imbalance on the shape of the output current ripple at  $D_c$  is similar to the one in multilevel MC-VSCs. Thus, without loss of generality, the subsequent analyses are performed for multilevel MC-VSCs, but the conclusions are easily applied also to interleaved MC-VSCs. This was verified by running simulations also for interleaved MC-VSCs converters, but the results are not included due to space limitations.

#### C. Modulating Signal Ripple

For regulating the output current of the MC-VSCs, proportional-integral or proportional-resonant controllers are widely used [1], [2], [13], [14]. They are designed so that the impact of the integral or the resonant action is bandlimited well-below the crossover frequency  $f_c$ . Consequently, at high frequencies, their frequency response converges to the one determined by the proportional gain. Thus, for these, high-frequency proportional-dominant controllers, the peak-peak value of the switching ripple component of the modulating signal,  $\Delta m_{pp}$ , can be very closely approximated as proportional to the relative crossover frequency  $f_{cr}$  of the current loop [26]. Moreover, since at  $D_c$ ,  $\Delta I \propto \Delta E$ ,  $\Delta m_{pp}$  at  $D_c$  is proportional to the relative imbalance magnitude,  $\Delta E_r$ ,

$$\Delta m_{pp} \approx \frac{k_p \Delta I}{K} \propto \frac{f_c}{N f_{pwm}} \frac{\Delta E}{E_n} = f_{cr} \Delta E_r$$

(7)

where  $k_p = 2\pi f_c L$  is the proportional gain of the current controller. Thus, the nonlinear effects of MSMU-PS-DPWM in unbalanced MC-VSCs, caused by the ripple in m, can be analyzed in a relative manner, by changing only  $\Delta E_r$  and  $f_{cr}$ .

Note that, in addition to  $\Delta E_r$  and  $f_{cr}$ , the time delay present in the propagation path of switching and feedback signals also impacts the modulator nonlinearities. Namely, by shifting the position of the modulating signal ripple with respect to the carriers, delay affects the types of intersections between m and  $w_i$  [27].

# IV. ANALYSIS OF MSMU-PS-DPWM NONLINEARITIES IN UNBALANCED MULTI-CELL CONVERTERS

#### A. Modulator Transcharacterisation

One way to describe the behavior of the modulator is a static transcharacteristic [27], which, in case of PS-DPWM, has to be defined for each carrier separately. The transcharacteristic of DPWM<sub>i</sub> provides the value of  $D_i$ , as a function of the average value of the modulating signal over one switching period, < m>, calculated as an average of  $N_{ms}$  values of  $m_s$  within one  $T_{pwm}$ . In Fig. 3 this corresponds to  $\frac{m_{s1}+m_{s2}+m_{s3}+m_{s4}}{4}$ .

The transcharacteristic of DPWM<sub>i</sub> is a piecewise linear function, with different gains  $k_i = \frac{dD_i}{d < m >}$  of each linear segment, determined by different types of intersections between m and  $w_i$ . In this article,  $k_i$  is referred to as the gain of DPWM<sub>i</sub>. In case of horizontal intersections between mand  $w_i$ ,  $D_i$  is determined by a unique modulating signal and both edges of  $x_i$  are equally modulated by applying a small perturbation of the modulating signal, d < m >. Thus, linear behavior of DPWM<sub>i</sub> is achieved and  $k_i \approx 1$ , as shown in Fig. 6a. Note that in presence of an imbalance,  $k_i$  is not exactly equal to 1 due to the ripple modulation effect [26]. Vertical intersections between m and  $w_i$  cause the gain of DPWM<sub>i</sub> to deviate from  $k_i \approx 1$  [27]. Counter-phase vertical intersections can occur for one or both slopes of  $w_i$ , preventing thereby the modulation of one or both edges of  $x_i$ . This results in reduced- or zero-gain (dead-band) zones [26] in the transcharacteristic of DPWM<sub>i</sub>, which, as shown in Fig. 6b and 6c, feature  $k_i \approx \frac{1}{2}$  and  $k_i = 0$ . The logic that prevents multiple commutations turns the in-phase "vertical" intersections into horizontal ones, which brings another nonlinear phenomenon. Namely, as explained in Section II.C, a small perturbation d < m > causes the response of one or both edges of  $x_i$  to be determined by the modulating signal discontinuity, instead of d < m >, resulting in increased gain of DPWM<sub>i</sub>. The inphase "vertical" intersections can appear for both slopes of  $w_i$ , or in combination with a horizontal or counter-phase vertical intersection. With in-phase operation, there is a range of duty cycles for which the steady-state cannot be achieved and thus, the transcharacteristics are not defined [34]. However, to indicate their impact, the corresponding nonlinearity zones are represented by vertical lines  $(k_i \to \infty)$ , as shown in Fig. 6d. These zones are referred to as infinite-gain (jitter) zones [27], because they result in LCOs, which have an adverse effect in MC-VSCs with either dc or ac operating point, as demonstrated in simulations (Fig. 14 and Fig. 21) and experiments (Fig. 19 and Fig. 20).

## B. Discontinuities of Critical Modulating Segments

Since the vertical intersections occur to an extent determined by the discontinuity of m [27], in order to quantify the

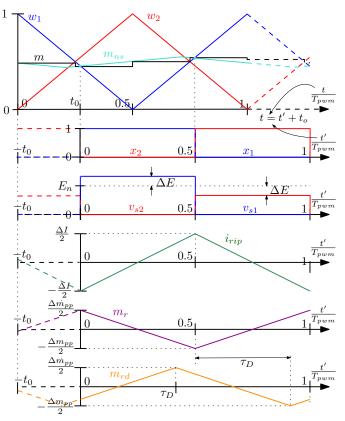

Fig. 7: Illustration of the procedure used to obtain modulating signal ripple component,  $m_{rd}(t)$ , naturally-sampled equivalent of the modulating signal  $m_{ns}(t)$  and its re-sampled variant. Illustration is given at  $D_c = \frac{1}{2}$ , for a MC-VSC with N=2 and the imbalance from (3). A purely proportional current controller is assumed and the relative delay is equal to  $\tau_D$ .

actuator (modulator) nonlinearity induced by them, it is of interest to define the critical modulating segments and their discontinuities.

Similarly to the definitions in [27], [34], the critical modulating segments of  $DPWM_i$  are defined as the two subsequent segments of m before and after the update instant closest to the intersection between m and  $w_i$ . For each  $DPWM_i$ , two pairs of critical modulating segments exist, each corresponding to one of the slopes of  $w_i$ .

The discontinuities of DPWM<sub>i</sub>'s critical modulating segments for positive ( $\Delta m_{icu}$ ) and negative ( $\Delta m_{icd}$ ) slopes of  $w_i$  are then defined as in [27]

$$\Delta m_{icu} = m \left( T_{icu} + \epsilon \right) - m \left( T_{icu} - \epsilon \right)$$

$$\Delta m_{icd} = m \left( T_{icd} - \epsilon \right) - m \left( T_{icd} + \epsilon \right)$$

(8)

where  $\epsilon$  is an infinitely small positive number,  $T_{icu}$  and  $T_{icd}$  are the modulating signal update instants closest to the intersection with  $w_i$ . Eq. (8) is defined such that positive values of  $\Delta m_{icu,d}$  correspond to in-phase operation.

The size of  $\Delta m_{icu,d}$  is correlated with the extension of nonlinear zones that appear in DPWM<sub>i</sub>'s transcharacteristics around  $D_c$ . The in-phase discontinuities of each slope of  $w_i$  contribute to its respective jitter zone heights as  $\delta_{i\infty u,d} = \frac{\Delta m_{icu,d}}{2}$  [27]. As verified in the following sections, when the in-phase operation occurs for both slopes of  $w_i$ , the joined

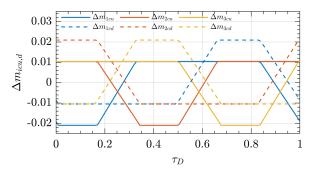

Fig. 8: Discontinuity graphs at  $D_c = \frac{1}{2}$  for a MC-VSC with N = 2,  $f_{cr} = 0.1$  and various imbalances: (a) DPWM<sub>1</sub>; (b) DPWM<sub>2</sub>.

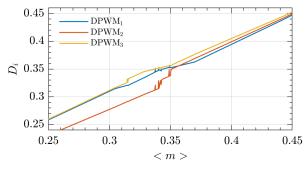

Fig. 10: Simulated transcharacteristics around  $D_c = \frac{1}{2}$  for MC-VSC with  $N=2, f_{cr}=0.1, \tau_D=0$  and various imbalances (a) DPWM<sub>1</sub> (b) DPWM<sub>2</sub>.

Fig. 9: Discontinuity graphs at  $D_c=\frac{1}{3}$  for a MC-VSC with N=3,  $f_{cr}=0.1$ , imbalance distribution from (3) and  $\Delta E_r=0.2$ . The blue, red and yellow colors correspond to DPWM<sub>1,2,3</sub>, respectively.

Fig. 11: Simulated transcharacteristics around  $D_c=\frac{1}{3}$  for a MC-VSC with  $N=3,\,f_{cr}=0.1,\,\tau_D=0$ , imbalance distribution from (3) and  $\Delta E_r=0.2$ . The blue, red and yellow colors correspond to DPWM<sub>1,2,3</sub>, respectively.

height of the jitter zones can be estimated as

$$\Delta D_{i\infty} = \frac{\Delta m_{icu}}{2} + \frac{\Delta m_{icd}}{2}.$$

(9)

Thus, it is of interest to provide a simple analytical procedure which would, for each DPWM<sub>i</sub>, predict whether an in-phase or counter-phase operation occurs, as well as the size of the  $\Delta m_{icu,d}$  around  $D_c$ .

#### C. Analytical Calculation of the Discontinuities

In order to calculate  $\Delta m_{icu,d}$ , it is necessary to find m(t). The exact analytical calculation of m(t) requires an iterative procedure, whose steps for two-level VSCs are described in [26], [27]. Since its extension to MC-VSCs brings additional complexity, in this article, an approximate procedure

is used, which is based on the naturally sampled equivalent of the modulating signal,  $m_{ns}(t)$  [27]. As shown in [27], the use of the approximate procedure is justified for predicting  $\Delta m_{icu,d}$ , since, for the high-frequency proportional-dominant controllers, its results negligibly deviate from those of the exact procedure. To obtain  $m_{ns}(t)$ , the analog equivalent of the modulating signal ripple,  $m_{rd}(t)$ , has to be found. The procedure relies on an assumption that all control blocks can be represented in s-domain.

For the assumed imbalance distribution (3) and the operating point (1), the converter circuit is solved for all topological states, considering only the average value of the modulating signal (as in Fig. 5). The resulting triangular ripple of the inductor current  $i_{rip}(t)$  is then found. Next,  $i_{rip}(t)$  is used to

solve a set of controller-related equations, which, after scaling by K, yields  $m_r(t)$ . Finally, an arbitrary amount of time delay  $\Delta t = \tau_D T_{pwm}$  is added to obtain  $m_{rd}(t)$ . This time delay can be due to the algorithm execution time, feedback filters, delays in the sensing and driver circuits, etc.

Based on  $m_{rd}(t)$  and the operating point considered, the naturally sampled modulating signal  $m_{ns}(t)$  is calculated relative to the first carrier [26]. This waveform is then used to find an approximate version of m(t), obtained by resampling  $m_{ns}(t)$  at assumed sampling instants. This approximation only slightly shifts the switching instants with respect to the exact calculation. The procedure described above is illustrated in Fig. 7 for a MC-VSC with N=2, the imbalance from (3) and the purely proportional current controller. The resampled version of  $m_{ns}(t)$  is used to calculate  $\Delta m_{icu,d}$ , as in (8). More details about the analytical calculation of the modulating signal discontinuities can be found in [26], [27], [35], [41], and in the MATLAB script discont\_calculation.m that is submitted with this article, as supplementary material.

#### D. Discontinuity Graphs

This section presents discontinuity graphs that provide the value of  $\Delta m_{icu,d}$  as a function of  $\tau_D$ . Note that with the above described procedure for analytical calculation of the modulating signal discontinuities, it is sufficient to obtain the discontinuity graph only for the first carrier. Namely, by simply shifting it for the value equal to the phase-shift of the considered carrier, the discontinuity graphs for all the other carriers can be obtained. The MATLAB script discont\_graphs.m used to obtain the discontinuity graphs is uploaded as active content with the article, to provide more insight.

The discontinuity graphs are given for  $\tau_D \in [0,1]$ , which is sufficient due to the periodicity of the switching ripple. The impact of  $\Delta E_r$  on  $\Delta m_{icu,d}$  is also illustrated. As predicted by (7), influence of  $f_{cr}$  is verified to be the same as that of  $\Delta E_r$ . For the presentation conciseness, the results below are obtained for fixed  $f_{cr} = 0.1$ .

Although vertical intersections also appear in the vicinity of  $D_c$ , the discontinuity graphs are plotted only at  $D_c$ , since, as shown below, this is sufficient to predict properties of MSMU-PS-DPWM transcharacteristics around  $D_c$ . Note that, with the imbalance distribution from (3), the discontinuity graphs at  $D_c$  for the positive slope of  $w_i$  are the same as the graphs at  $1-D_c$  for the negative slope of  $w_i$ .

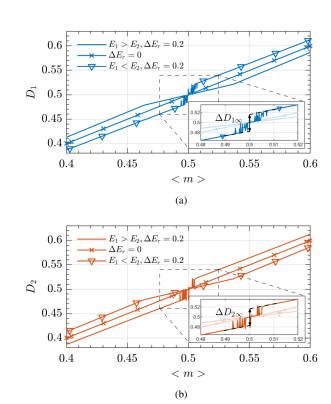

In Fig. 8, the discontinuity graphs for N=2 and  $D_c=\frac{1}{2}$  are shown for various imbalances. Since for  $D_c=\frac{1}{2}$ ,  $D_c=1-D_c$ , the discontinuity graphs for the positive and negative slopes of  $w_i$  are the same. The presented discontinuity graphs are proportional to  $\Delta E_r$ , as implied by (7). Under balanced conditions, i.e., for  $\Delta E_r=0$ , the calculated discontinuities are zero and thus the vertical intersections are not possible in the steady-state. Also, it is seen from Fig. 8 that the borders between the in-phase and counter-phase regimes are almost

TABLE I: Hardware and Control Parameters of the Tested MC-VSCs

| MC-VSC                   | label     | value          | unit             |

|--------------------------|-----------|----------------|------------------|

| Number of cascaded cells | N         | $\{2, 3\}$     | /                |

| Nominal dc link voltage  | $E_n$     | $\{120, 50\}$  | V                |

| Filter inductance        | L         | 1.5            | mΗ               |

| Output capacitance       | C         | 470            | $\mu \mathrm{F}$ |

| Output resistance        | R         | 24             | Ω                |

| Switching frequency      | $f_{pwm}$ | 10/N           | kHz              |

| Dead-time                | $t_{dt}$  | 0.8            | $\mu$ s          |

| Control loop             | label     | value          | unit             |

| Sampling frequency       | $f_s$     | 20             | kHz              |

| Crossover frequency      | $f_c$     | $\{1, 0.5\}$   | kHz              |

| Proportional gain        | $k_p$     | $\{9.6, 4.7\}$ | $\Omega$         |

| Integral / resonant gain | $k_i$     | $\{5.9, 1.5\}$ | kΩ/s             |

independent of  $\Delta E_r$ . The same is verified for  $f_{cr}$ . Based on this, it can be inferred that, for the fixed imbalance distribution,  $\tau_D$  defines whether the in-phase or counter-phase regime occurs, whereas the extent of the discontinuities is determined by  $\Delta E_r$  and  $f_{cr}$ . Moreover, for the value of  $\tau_D$  corresponding to the above mentioned border, almost linear behaviour of the modulator is achieved, regardless of  $\Delta E_r$  and  $f_{cr}$ . Another important remark from Fig. 8, is that the discontinuity graphs of DPWM1 are equal to the inverted graphs of DPWM2. This is due to PS-DPWM, which causes the discontinuity graphs of adjacent carriers to feature the same shape, with  $\tau_D$ -axis shifted by the imposed phase-shift, i.e.,  $\frac{1}{N}$ .

In Fig. 9, the discontinuity graphs for N=3,  $D_c=\frac{1}{3}$ and the imbalance distribution from (3) are shown. For the sake of presentation, only the results for  $\Delta E_r = 0.2$  are plotted, but it is verified that, as for N=2, the values of the discontinuities are proportional to  $\Delta E_r$  and  $f_{cr}$ , while the boundaries between in-phase and counter-phase regimes remain located at nearly constant values of  $\tau_D$ . From Fig. 9, it can be seen that the sum of maximum discontinuities for the positive and negative slope of  $w_i$  is the same for all DPWMs and reduced, compared to N=2. This is an important remark, which underlines that as N increases, the discontinuity-related nonlinear effects of MSMU-PS-DPWM in unbalanced MC-VSCs are reduced. Note that this was also verified for N > 3, but the results are not included due to space limitations. In addition, given that the discontinuity related modulator nonlinearity is more pronounced for lower values of N, the results in this article are presented for such values of N. For a very high number of cells, i.e., multi-sampling factors, the discontinuities and, consequently, the non-linear effects caused by them, are almost completely suppressed, as the sampled feedback closely resembles the continuous analog signal [27].

#### E. Simulated Transcharacteristics

In order to verify the predictions of the discontinuity graphs, simulations are performed to obtain the transcharacteristics of MSMU-PS-DPWM around  $D_c$ . For this purpose, MC-VSCs with the parameters from Table I are implemented in MATLAB / Simulink. The transcharacteristics are obtained

<sup>&</sup>lt;sup>6</sup>In addition to time delay, the intersections between the modulating waveform and the carriers can also be influenced by feedback filters, as shown in [34]. However, the time delay was found to be of more general value, not having to consider a specific filter design.

Fig. 12: Simulated transcharacteristics around  $D_c=\frac{2}{3}$  for a MC-VSC with N=3,  $\tau_D=\frac{1}{N}$ ,  $f_{cr}=0.1$  and (a) balanced dc links  $E_1=E_2=E_3=E_n$ ; (b) an arbitrarily chosen imbalance distribution:  $E_1=1.23E_n$ ,  $E_2=0.86E_n$ ,  $E_3=0.91E_n$ . The blue, red and yellow colors correspond to DPWM<sub>1,2,3</sub>, respectively.

by imposing a slow current reference sweep while saving the values of the modulating signal  $m_s$  and the detected duty cycles  $D_{1...N}$ . The Simulink model sim\_trch.slx and the post-processing script plot\_trch.m used to obtain simulated transcharacteristics are submitted with this article, as active content.

In Fig. 10 simulated transcharacteristics around  $D_c = \frac{1}{2}$  are shown for N=2,  $\tau_D=0$ ,  $f_{cr}=0.1$ , considering  $E_1>E_2$ and  $E_1 < E_2$ , both with  $\Delta E_r = 0.2$ . The results for  $\Delta E_r = 0$ are also included to verify that MSMU-PS-DPWM is linear under balanced conditions. As predicted by the discontinuity graphs in Fig. 8, for  $E_1 > E_2$ , the transcharacteristics of DPWM<sub>1</sub> and DPWM<sub>2</sub> exhibit reduced-gain and jitter zones, respectively, while vice versa is observed for  $E_1 < E_2$ . Under unbalanced conditions, jittering of the detected duty cycle, caused by the LCOs, is clearly observable. In addition, the transcharacteristics of DPWM<sub>1</sub> and DPWM<sub>2</sub>, obtained for  $E_1 < E_2$ , are respectively equal to those of DPWM<sub>2</sub> and DPWM<sub>1</sub>, obtained for  $E_1 > E_2$ . Furthermore, the heights of the joined jitter zones in Fig. 10,  $\Delta D_{1\infty} = \Delta D_{2\infty} = 0.032$ , are the same as those calculated from (9), by substituting  $\Delta m_{icu,d}$  predicted by the graphs in Fig. 8.

In Fig. 11 simulated transcharacteristics around  $D_c=\frac{1}{3}$  are shown for N=3,  $\tau_D=0$ ,  $f_{cr}=0.1$ , imbalance distribution from (3), and  $\Delta E_r=0.2$ . As predicted by the discontinuity graphs in Fig. 9, the transcharacteristics of DPWM<sub>1</sub> and DPWM<sub>2</sub> exhibit reduced-gain and jitter zones, respectively, whereas for DPWM<sub>3</sub> both reduced-gain and jitter zones are present. Note that in addition to the LCOs observed around the jitter zones in the transcharacteristic of the DPWM<sub>i</sub> that features an in-phase operation, some smaller amplitude LCOs

are also visible in the transcharacteristics of all other DPWMs. This is because LCOs, caused by the in-phase operation of DPWM<sub>i</sub>, are present in the system and thus, also impact the operation of other DPWMs. This is an important remark that demonstrates that in-phase operation for one carrier is sufficient to cause jittering in the overall system. Moreover, since, as mentioned in Section II.B, a counter-phase operation for one carrier is at the same time an in-phase operation for another carrier, vertical intersections in unbalanced MC-VSCs with MSMU-PS-DPWM always cause jittering. This conclusion is valid regardless of the imbalance distribution, and, as shown in the following section, the jittering effect is more pronounced for higher  $\tau_D$  and  $f_{cr}$ .

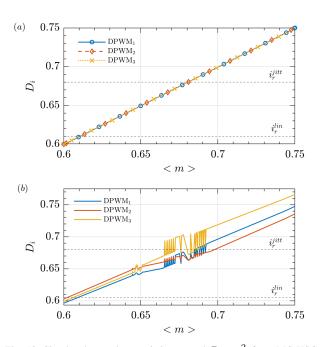

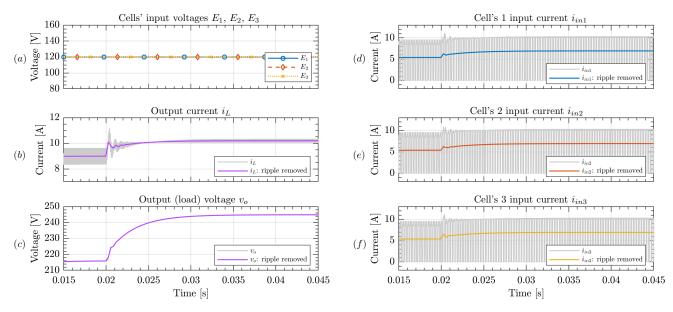

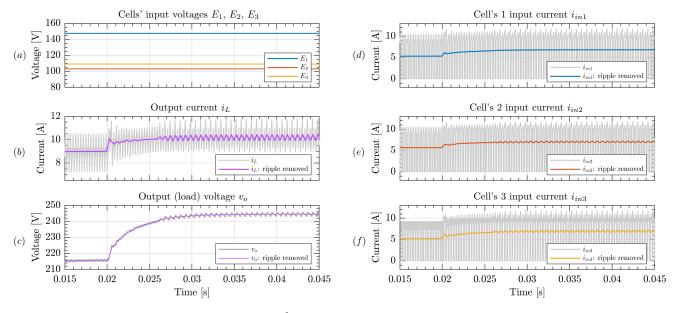

To further elaborate on this, in Fig. 12 simulated transcharacteristics around  $D_c = \frac{2}{3}$  are shown for N = 3,  $\tau_D = \frac{1}{N}$ ,  $f_{cr} = 0.1$  and (a) balanced dc links:  $E_1 = E_2 =$  $E_3 = E_n$ ; (b) an arbitrarily chosen imbalance distribution:  $E_1 = 1.23E_n$ ,  $E_2 = 0.86E_n$ ,  $E_3 = 0.91E_n$ . As expected, under balanced conditions, linear behaviour of MSMU-PS-DPWM is achieved. However, in presence of an arbitrarily chosen imbalance, the nonlinear effects are clearly visible, which shows that the nonlinearity of MSMU-PS-DPWM is present regardless of the imbalance distribution. To illustrate its detrimental impact on the performance of the MC-VSC, the reference step change is imposed, which in presence of imbalance moves the operating point from linear to jitter zone (as marked in Fig. 12). Time domain input and output converter waveforms in response to this reference change are shown in Fig. 13 under balanced ( $E_1 = E_2 = E_3 = E_n$ ) and in Fig. 14 under unbalanced conditions ( $E_1 = 1.23E_n$ ,  $E_2 =$  $0.86E_n$ ,  $E_3 = 0.91E_n$ ). In addition to the raw waveforms (shown in gray color in Fig. 13 (b)-(f) and Fig. 14 (b)-(f)), the waveforms obtained after removing the switching ripple (using a moving average filter over  $T_{pwm}$ ) are also shown, for a better visualization. After the step reference change, under balanced conditions (Fig. 13) the steady-state is achieved and the responses are as expected. However, in presence of imbalance (Fig. 14), the steady-state cannot be achieved and the LCOs, caused by the nonlinearity of MSMU-PS-DPWM, are clearly visible in the converter waveforms, which is in accordance with the corresponding transcharacteristics from Fig. 12 (b).

# V. EXPERIMENTAL VALIDATION

This section provides experimental validation of the previously discussed nonlinear phenomena observed in unbalanced MC-VSCs with MSMU-PS-DPWM and illustrates their influence in typical application scenarios. For dc-dc converters, the impact on the transient response and the occurrence of LCOs is examined. For dc-ac converters, the impact on the output waveform distortion is analyzed.

# A. Test Setup

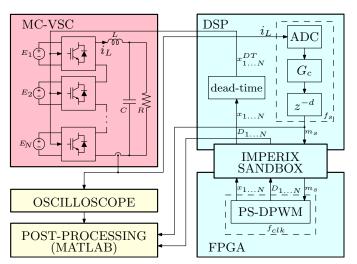

For the experimental measurements, a single-phase currentcontrolled laboratory prototype of the MC-VSC from Fig. 2 is realized, with the hardware and control loop parameters from Table I. The block diagram and the picture of the test setup

Fig. 13: Simulation results for a MC-VSC with N=3,  $\tau_D=\frac{1}{N}$ ,  $f_{cr}=0.1$  and balanced dc links:  $E_1=E_2=E_3=E_n$ . Input and output converter waveforms in response to the reference step change from  $i_r^{lin}$  to  $i_r^{jitt}$  (marked in Fig. 12), which in presence of imbalance moves the operating point from linear to jitter zone: (a) cell's input voltages, (b) output current, (c) output (load) voltage and (d)-(f) cell's input currents. For a better visualization, in addition to the raw waveforms (shown in gray color in (b)-(d)), the waveforms after removing switching ripple are also shown.

Fig. 14: Simulation results for a MC-VSC with N=3,  $\tau_D=\frac{1}{N}$ ,  $f_{cr}=0.1$  and an arbitrarily chosen imbalance distribution:  $E_1=1.23E_n$ ,  $E_2=0.86E_n$ ,  $E_3=0.91E_n$ . Input and output converter waveforms in response to the reference step change from  $i_r^{lin}$  to  $i_r^{jitt}$ , which moves the operating point from linear to jitter zone, as marked in Fig. 12 (a): (a) cell's input voltages, (b) output current, (c) output (load) voltage and (d)-(f) cell's input currents. For a better visualization, in addition to the raw waveforms (shown in gray color in (b)-(d)), the waveforms after removing switching ripple are also shown.

are shown in Fig. 15 and Fig. 16. The setup consists of three main parts, denoted by three different colors in Fig. 15. Red part represents the tested MC-VSC, realized using the SiC half-bridge modules from Imperix. An inductive filter is used and a resistive load is connected in parallel with the output capacitor. Inductor current is sensed by an external sensor from Imperix, which is based on LAH 50-P from LEM.

The control system, denoted by blue color in Fig. 15, is implemented on Imperix B-Box Embedded Control Module,

using both the DSP and FPGA that are available on the board. The ADC and the current control are implemented on DSP. Due to the algorithm computation time, the modulating signal update is delayed by one sampling period,  $T_s$ . An additional delay is added in some tests, to examine the impact of delay on the modulator nonlinearities, as analyzed in Section IV. The digital modulating signal,  $m_s$ , is forwarded to the FPGA via Imperix sandbox, which serves as an interface between DSP and FPGA, and ensures a proper synchronization. The

Fig. 15: Block diagram of the test setup used to experimentally validate nonlinear effects of MSMU-PS-DPWM in unbalanced MC-VSCs.

Fig. 16: Test-setup used for experimental validation. 1) Power supply TDK/Lambda GEN300-17 used for the dc-dc tests; 2) SiC half-bridge modules from Imperix; 3) Boom Box controller; 4) laptop; 5) power supplies GW GPC-3030 used for the dc-ac tests; 6) filter inductor, output capacitor and sensing circuits; 7) resistive load; 8) oscilloscope; power supplies 9) EA-PSI 9750-20TDK and 10) Keyisght RP7962A used for the dc-dc tests.

MSMU-PS-DPWM, is coded in VHDL and implemented on the FPGA, with the DPWM clock that runs at  $f_{clk}=125$  MHz. The switching signals,  $x_{1\dots N}$ , are sent back to DSP where dead-time is realized. In order to obtain modulator transcharacteristics, the duty cycles,  $D_{1\dots N}$  are detected on the FPGA, forwarded to DSP and exported together with  $m_s$ , using Imperix Cockpit. Post-processing, denoted by yellow color in Fig. 15, is performed in MATLAB. For examining transient response and waveform distortion, the inductor current is acquired with 12.5 MS/s rate, using the Tektronix TCP202 current probe and MS056 oscilloscope.

## B. Impact of Nonlinearities in DC-DC Converters

As examples of dc-dc converters, multilevel MC-VSCs with two and three half-bridge cells are formed. The dc link of each cell is realized using one of the following power supplies: Keyisght RP7962A, TDK/Lambda GEN300-17 and EA-PSI 9750-20. The nominal dc link voltage is set to  $E_n=120V$ . Proportional-integral current controller is used

$$G_c(z) = k_p + k_i T_s \frac{z}{z - 1} \tag{10}$$

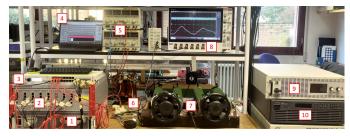

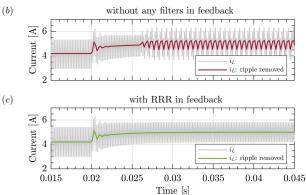

where  $k_p$ ,  $k_i$  are proportional and integral gain, respectively. In Fig. 17, the transcharacteristics, obtained by imposing current reference sweep in experiments and simulations, are shown around  $D_c=\frac{1}{2}$ , for the MC-VSC with N=2, imbalance distribution from (3) and different  $\tau_D$ ,  $f_{cr}$  and  $\Delta E_r$ . According to the presented results, an excellent match between simulations and experiments is achieved. Moreover, the types of zones and the joined jitter zone heights that appear in Fig. 17a, 17b and 17d correspond to those predicted by the discontinuity graphs in Fig. 8. Compared to Fig. 17a, the extensions of the nonlinear zones in Fig. 17c and 17d are halved, which is in agreement with (7).

In the presented simulated and experimentally measured transcharacteristics the impact of LCOs on system inability to achieve steady-state operation is seen, around the operating points where nonlinearity zones exist. This causes a stochastic jittering of the duty cycle. The degree of this jittering depends on the LCOs' magnitude and frequency and should not be misinterpreted with the height of the jitter zone, which quantifies the extent of the actuator (modulator) nonlinearity. Note that it is also experimentally verified that under balanced conditions, i.e., for  $\Delta E_r = 0$ , linear transcharacteristics are obtained, but the results are not included due to space limitations.

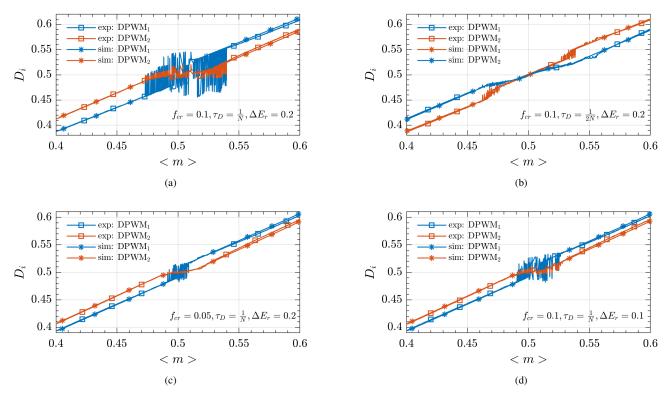

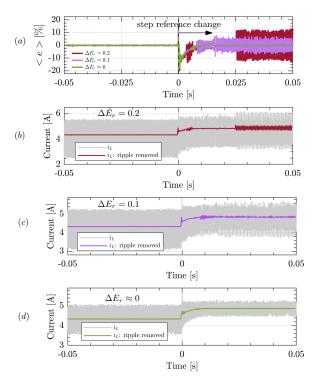

In Fig. 18 and Fig. 19 the experimental results are shown for the MC-VSC with  $N=3, f_{cr}=0.1, \tau_D=\frac{1}{N}$ , imbalance distribution from (4) and different  $\Delta E_r$ . Comparison between simulated and experimentally measured transcharacteristics around  $D_c = \frac{1}{3}$  is shown in Fig. 18a and 18b for  $\Delta E_r = 0.2$ and  $\Delta E_r = 0.1$ , respectively. An excellent match between simulations and experiments is achieved. Moreover, the extent of the observed nonlinear effects is again scaled with  $\Delta E_r$ . In Fig. 19, the effect of jittering and LCOs is illustrated in time-domain. A step reference change is imposed, so that, for  $\Delta E_r \neq 0$ , the operating point changes from linear to jitter zone, as marked in Fig. 18a and 18b. The tracking errors, relative to the maximum peak-peak current ripple present under balanced conditions, are shown in Fig. 19 (a) for  $\Delta E_r \in \{0, 0.1, 0.2\}$ . For a better visualization, switching ripple is removed from the plotted data using a moving average filter over  $T_{pwm}$ . As expected, with unbalanced dc links, the steady-state can not be achieved after the step reference change and the LCOs, caused by the modulator nonlinearity, are clearly visible in the presented waveforms. On the contrary, balanced dc links yield a linear operation. This is further illustrated in Fig. 19 (b)-(d) where the inductor current in response to the same reference step change is shown for  $\Delta E_r \in \{0, 0.1, 0.2\}$ . In addition to the raw, unprocessed, data that is acquired by the oscilloscope and shown in gray color in Fig. 19 (b)-(d), the waveforms obtained after removing the switching ripple are also shown, for a better visualization.

# C. Impact of Nonlinearities in DC-AC Converters

As an example of dc-ac converter, a multilevel MC-VSC with two full-bridge cells is formed. The linear power supplies GW GPC-3030 are used as the cells' dc inputs, to avoid stability problems of the switched power supplies that were noticed under unbalanced dc links and ac operation. Nominal dc link voltage is set to  $E_n=50$  V, which was the maximum possible due to hardware limitations of the power supplies.

In order to investigate the impact of the previously discussed phenomena on the output waveform distortion, a sinusoidal

Fig. 17: Comparison between experimentally measured and simulated transcharacteristics around  $D_c=\frac{1}{2}$  for the MC-VSC with N=2, imbalance distribution from (3) and different  $\tau_D$ ,  $f_{cr}$  and  $\Delta E_r$ : (a)  $f_{cr}=0.1$ ,  $\tau_D=\frac{1}{N}$ ,  $\Delta E_r=0.2$ ; (b)  $f_{cr}=0.1$ ,  $\tau_D=\frac{1}{2N}$ ,  $\Delta E_r=0.2$ ; (c)  $f_{cr}=0.05$ ,  $\tau_D=\frac{1}{N}$ ,  $\Delta E_r=0.2$ ; (d)  $f_{cr}=0.1$ ,  $\tau_D=\frac{1}{N}$ ,  $\Delta E_r=0.1$ .

ac reference is imposed and the proportional-resonant current controller is used

$$G_c(z) = k_p + k_i T_s \frac{1 - \cos(2\pi f_1 T_s) z^{-1}}{1 - 2\cos(2\pi f_1 T_s) z^{-1} + z^{-2}}$$

(11)

where  $f_1 = 50$  Hz is the fundamental frequency. Due to RLC load, at  $f_1$ , the output voltage lags the inductor current for  $21^{\circ}$ . Note that the simulations were performed also with an inductive filter directly connected to an ac voltage source, and the conclusions remain the same as below.

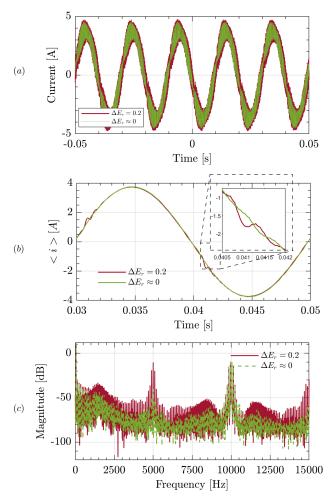

At first, the transcharacteristics are measured around  $D_c =$  $\frac{1}{2}$  for  $f_{cr}=0.1,~\tau_D=\frac{1}{N},$  imbalance distribution from (3) and  $\Delta E_r \in \{0, 0.2\}$ . The results are confirmed to be similar to the ones of the previously tested MC-VSC with half-bridge cells. For  $\Delta E_r = 0.2$ , the jittering occurs, same as in Fig. 17a, which is expected to cause distortion in ac operation. On the other hand, since MSMU-PS-DPWM yields linear operation under balanced conditions, the dead-time is expected to be the only source of distortion in ac operation with  $\Delta E_r = 0$ . To verify this, the time-domain waveforms of the inductor current and their spectra are compared in Fig. 20 for  $\Delta E_r = 0.2$ and  $\Delta E_r = 0$ . For a better visualization, in Fig. 20 (b) the switching ripple is removed from plotted data using a MAF over  $T_{pwm}$ . As expected, a considerable distortion around the voltage zero crossings occurs for  $\Delta E_r = 0.2$ , which is not present for  $\Delta E_r = 0$ . Note that the similar effects were observed in simulations with zero dead-time, which verifies that the origin of the distortion for  $\Delta E_r = 0.2$  is the modulator nonlinearity.

## VI. CONCLUSIONS

In this paper, the discontinuity-related nonlinear effects of MSMU-PS-DPWM that arise in unbalanced MC-VSCs are analyzed. A simple analytical procedure is proposed to predict the nonlinear zones that appear in the transcharacteristic of each carrier. Their extension is verified to be proportional to the relative value of imbalance magnitude and crossover frequency, and inversely proportional to the number of cells. It is shown that, due to PS-DPWM, vertical intersections in MSMU unbalanced MC-VSCs always cause LCOs. This phenomenon, which is more pronounced for higher control-loop delays and bandwidths, deteriorates the performance of dc-dc and dc-ac MC-VSCs. Experimental measurements, performed on single-phase laboratory prototypes of three- and four-level MC-VSCs, are in excellent agreement with simulations and analytical predictions.

## **APPENDIX**

To avoid detrimental impact of discontinuity-related non-linear effects of MSMU-PS-DPWM that appear in unbalanced MC-VSCs, some provision has to be taken in practical applications. Since the modulator non-linearity arises due to the switching ripple that gets sampled in presence of an imbalance between the cells, digital feedback filtering aimed at

Fig. 18: Experimental results for the MC-VSC with  $N=3, f_{cr}=0.1, \tau_D=\frac{1}{N},$  imbalance distribution from (4) and  $\Delta E_r\in\{0,0.1,0.2\}.$  Comparison between simulated and experimentally measured transcharacteristics for (a)  $\Delta E_r=0.2;$  (b)  $\Delta E_r=0.1.$

removing the ripple from the acquired feedback signal seems like a promising candidate. Though moving average filter over  $T_{pwm}$  is known to be effective in removing the switching ripple in multi-sampled applications, it compromises dynamic performance improvements that increased sampling frequency offers [17], [35], [41]. As an alternative, this article proposes repetitive ripple removal filter (RRR) from [36]. Its z-domain transfer function is

$$G_{RRR}(z) = \frac{(1+R)\left(1 - \left(z^{-N_{ms}} - \frac{1}{N_{ms}}\sum_{q=1}^{N_{ms}}z^{-q}\right)\right)}{1 - \left(z^{-N_{ms}} - \frac{1}{N_{ms}}\sum_{q=1}^{N_{ms}}z^{-q}\right) + R}$$

where R defines the settling time and the phase-lag of the RRR [36]. In this article, R=0.125 is used, such that RRR's settling time is approximately  $10T_{pwm}$  and that its impact on control loop's small-signal dynamics of interest is negligible [36].

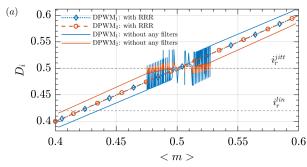

To demonstrate effectiveness of RRR in mitigating the non-linear effects discussed in this article, simulations were run for MC-VSC with N=2,  $f_{cr}=0.1$ ,  $\tau_D=\frac{1}{N}$ , imbalance from (3) and  $\Delta E_r=0.2$ . Simulations were organized in the same way and with the same parameters as outlined at the beginning of Section IV.E. In Fig. 21 (a) modulator transcharacteristics are compared for the case without any filters in feedback  $(G_{fb}(z)=1)$  and with RRR  $(G_{fb}(z)=G_{RRR}(z))$ . As seen, RRR successfully eliminates non-linear zones that are present when no filters are used, resulting in a completely linear behaviour of MSMU-PS-DPWM, even in presence of

Fig. 19: Experimental results for the MC-VSC with  $N=3, f_{cr}=0.1, \tau_D=\frac{1}{N}$ , imbalance distribution from (4) and  $\Delta E_r\in\{0,0.1,0.2\}$ . (a) Relative tracking errors of the reference step change from  $i_r^{lin}$  to  $i_r^{jit}$ , which for  $\Delta E_r \neq 0$ , moves the operating point from linear to jitter zone, as marked in Fig. 18a and 18b. The switching ripple is filtered out for a better visualisation. The tracking errors are given relative to the maximum peak-peak current ripple present under balanced conditions. (b), (c) and (d) Inductor current in response to the same reference step change.

an imbalance. To further elaborate on this, a step reference change is imposed, so that, in the case without any filters, the operating point moves from linear to jitter zone, as marked in Fig. 21 (a). Inductor current waveforms in response to this reference change are shown in Fig. 21 (b) and (c), in the case without any filters and with RRR in feedback. LCOs that are clearly observable in Fig. 21 (b) are successfully eliminated by RRR, as seen in Fig. 21 (c). This illustrates the effectiveness of RRR in mitigating the discontinuity-related non-linear effects of MSMU-PS-DPWM and, consequently, in preventing their detrimental impact on performance of unbalanced MC-VSCs.

## REFERENCES

- J. I. Leon, S. Vazquez, and L. G. Franquelo, "Multilevel converters: Control and modulation techniques for their operation and industrial applications," *Proceedings of the IEEE*, vol. 105, no. 11, pp. 2066–2081, 2017

- [2] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, "A survey on cascaded multilevel inverters," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 7, pp. 2197–2206, 2010.

- [3] B. Li, R. Yang, D. Xu, G. Wang, W. Wang, and D. Xu, "Analysis of the phase-shifted carrier modulation for modular multilevel converters," *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 297–310, 2015.

- [4] Y. Liang and C. Nwankpa, "A new type of STATCOM based on cascading voltage-source inverters with phase-shifted unipolar SPWM," *IEEE Transactions on Industry Applications*, vol. 35, no. 5, pp. 1118– 1123, 1999.

Fig. 20: Experimental results for the MC-VSC with N=2,  $f_{cr}=0.1$ ,  $\tau_D=\frac{1}{N}$ , imbalance from (3) and  $\Delta E_r\in\{0,0.2\}$ , operated in sinusoidal ac regime: time domain waveforms of the inductor current, (a) with and (b) without the switching ripple; (c) spectra of the inductor current.

- [5] I. Z. Petric, R. K. Iyer, N. C. Brooks, and R. C. N. Pilawa-Podgurski, "A real-time estimator for capacitor voltages in the flying capacitor multilevel converter," in 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL), 2022, pp. 1–8.

- [6] G. Bonanno and L. Corradini, "Digital predictive current-mode control of three-level flying capacitor buck converters," *IEEE Transactions on Power Electronics*, vol. 36, no. 4, pp. 4697–4710, 2021.

- [7] O. Garcia, P. Zumel, A. de Castro, and A. Cobos, "Automotive dc-dc bidirectional converter made with many interleaved buck stages," *IEEE Transactions on Power Electronics*, vol. 21, no. 3, pp. 578–586, 2006.

- [8] Y. Qiu, M. Xu, K. Yao, J. Sun, and F. Lee, "Multifrequency small-signal model for buck and multiphase buck converters," *IEEE Transactions on Power Electronics*, vol. 21, no. 5, pp. 1185–1192, 2006.

- [9] P.-W. Lee, Y.-S. Lee, D. Cheng, and X.-C. Liu, "Steady-state analysis of an interleaved boost converter with coupled inductors," *IEEE Trans*actions on *Industrial Electronics*, vol. 47, no. 4, pp. 787–795, 2000.

- [10] D. Holmes and B. McGrath, "Opportunities for harmonic cancellation with carrier-based PWM for a two-level and multilevel cascaded inverters," *IEEE Transactions on Industry Applications*, vol. 37, no. 2, pp. 574–582, 2001.

- [11] Y. Li, Y. Wang, and B. Q. Li, "Generalized theory of phase-shifted carrier pwm for cascaded H-bridge converters and modular multilevel converters," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 2, pp. 589–605, 2016.

- [12] G. Walker and G. Ledwich, "Bandwidth considerations for multilevel converters," *IEEE Transactions on Power Electronics*, vol. 14, no. 1, pp. 74–81, 1999.

- [13] J. Ma, X. Wang, F. Blaabjerg, W. Song, S. Wang, and T. Liu, "Mul-

Fig. 21: Comparison of simulation results for MC-VSC with N=2,  $f_{cr}=0.1$ ,  $\tau_D=\frac{1}{N}$ , imbalance from (3) and  $\Delta E_r=0.2$ , in case without any filters in feedback and with repetitive ripple removal filter (RRR): (a) modulator transcharacteristics around  $D_c=\frac{1}{2}$ ; (b) inductor current in response to the step reference change that, in case without any filters in feedback, moves the operating point from linear to jitter zone, as indicated in (a).

- tisampling method for single-phase grid-connected cascaded H-bridge inverters," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 10, pp. 8322–8334, 2020.

- [14] S. He, D. Zhou, X. Wang, and F. Blaabjerg, "Multisampling control of two-cell interleaved three-phase grid-connected converters," in 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), 2021, pp. 1432–1437.

- [15] M. Odavic, V. Biagini, M. Sumner, P. Zanchetta, and M. Degano, "Multi-sampled carrier-based pwm for multilevel active shunt power filters for aerospace applications," in 2011 IEEE Energy Conversion Congress and Exposition, 2011, pp. 1483–1488.

- [16] J. I. Y. Ota, Y. Shibano, N. Niimura, and H. Akagi, "A phase-shifted-PWM D-STATCOM using a modular multilevel cascade converter (SSBC)—part I: Modeling, analysis, and design of current control," *IEEE Transactions on Industry Applications*, vol. 51, no. 1, pp. 279–288, 2015.

- [17] R. Cvetanovic, I. Petric, P. Mattavelli, and S. Buso, "High Performance Multi-Sampled Control for Power Electronics Converters," in 2023 22nd International Symposium on Power Electronics (Ee), Oct. 2023.

- [18] R. Cvetanovic, I. Z. Petric, P. Mattavelli, and S. Buso, "Small-signal modeling of phase-shifted digital PWM in interleaved and multilevel converters," *IEEE Transactions on Power Electronics*, pp. 1–12, 2022.

- [19] X. Zhang and J. W. Spencer, "Study of multisampled multilevel inverters to improve control performance," *IEEE Transactions on Power Electronics*, vol. 27, no. 11, pp. 4409–4416, 2012.

- [20] H. Fujita, "A single-phase active filter using an H-bridge PWM converter with a sampling frequency quadruple of the switching frequency," *IEEE Transactions on Power Electronics*, vol. 24, no. 4, pp. 934–941, 2009.

- [21] G. Walker, "Digitally-implemented naturally sampled PWM suitable for multilevel converter control," *IEEE Transactions on Power Electronics*, vol. 18, no. 6, pp. 1322–1329, 2003.

- [22] H. Akagi, S. Inoue, and T. Yoshii, "Control and performance of a transformerless cascade PWM STATCOM with star configuration," *IEEE Transactions on Industry Applications*, vol. 43, no. 4, pp. 1041–1049, 2007.

- [23] A. Marquez, J. I. Leon, V. G. Monopoli, S. Vazquez, M. Liserre, and L. G. Franquelo, "Generalized harmonic control for CHB converters with unbalanced cells operation," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 11, pp. 9039–9047, 2020.

- [24] G. Farivar, B. Hredzak, and V. G. Agelidis, "Decoupled control system for cascaded H-bridge multilevel converter based STATCOM," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 1, pp. 322–331, 2016.

- [25] B. Liu, W. Song, Y. Li, and B. Zhan, "Performance improvement of dc capacitor voltage balancing control for cascaded H-bridge multilevel converters," *IEEE Transactions on Power Electronics*, vol. 36, no. 3, pp. 3354–3366, 2021.

- [26] L. Corradini and P. Mattavelli, "Modeling of multisampled pulse width modulators for digitally controlled dc-dc converters," *IEEE Transactions* on *Power Electronics*, vol. 23, no. 4, pp. 1839–1847, 2008.

- [27] I. Z. Petric, P. Mattavelli, and S. Buso, "Investigation of nonlinearities introduced by multi-sampled pulsewidth modulators," *IEEE Transactions on Power Electronics*, vol. 37, no. 3, pp. 2538–2550, 2022.

- [28] V. G. Monopoli, A. Marquez, J. I. Leon, M. Liserre, G. Buticchi, L. G. Franquelo, and S. Vazquez, "Applications and modulation methods for modular converters enabling unequal cell power sharing: Carrier variable-angle phase-displacement modulation methods," *IEEE Indus*trial Electronics Magazine, vol. 16, no. 1, pp. 19–30, 2022.

- [29] V. G. Monopoli, Y. Ko, G. Buticchi, and M. Liserre, "Performance comparison of variable-angle phase-shifting carrier pwm techniques," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 7, pp. 5272– 5281, 2018.

- [30] M. Caris, H. Huisman, J. Schellekens, and J. Duarte, "Generalized harmonic elimination method for interleaved power amplifiers," in IECON 2012 - 38th Annual Conference on IEEE Industrial Electronics Society, 2012, pp. 4979–4984.

- [31] M. L. A. Caris, H. Huisman, and J. L. Duarte, "Harmonic elimination by adaptive phase-shift optimization in interleaved converters," in 2013 IEEE Energy Conversion Congress and Exposition, 2013, pp. 763–768.

- [32] S. Waffler, J. Biela, and J. Kolar, "Output ripple reduction of an automotive multi-phase bi-directional dc-dc converter," in 2009 IEEE Energy Conversion Congress and Exposition, 2009, pp. 2184–2190.

- [33] S. Buso and P. Mattavelli, Digital Control in Power Electronics, 2nd Edition. Morgan & Claypool, 2015.

- [34] I. Z. Petric, P. Mattavelli, and S. Buso, "A jitter amplification phenomenon in multisampled digital control of power converters," *IEEE Transactions on Power Electronics*, vol. 36, no. 8, pp. 8685–8695, 2021.

- [35] L. Corradini, "Analysis and implementation of digital control architectures for dc-dc switching converters," Ph.D. dissertation, Dept. Inf. Eng., Univ. Padova, Padova, Italy, 2008.

- [36] L. Corradini, P. Mattavelli, E. Tedeschi, and D. Trevisan, "High-Bandwidth Multisampled Digitally Controlled DC-DC Converters Using Ripple Compensation," *IEEE Transactions on Industrial Electronics*, vol. 55, no. 4, pp. 1501–1508, Apr. 2008.

- [37] D. G. Holmes and T. A. Lipo, Pulse Width Modulation for Power Converters: Principles and Practice. New York, NY, USA: Wiley-IEEE Press, 2003.

- [38] I. Z. Petric, R. Cvetanovic, P. Mattavelli, and S. Buso, "Models for Stationary Noise Propagation in Multi-Sampled PWM Power Electronic Control Systems with Decimation," *IEEE Transactions on Power Elec*tronics, pp. 1–16, 2023.

- [39] R. Cvetanovic, I. Z. Petric, P. Mattavelli, and S. Buso, "Switching Noise Propagation and Suppression in Multi-sampled Power Electronics Control Systems," *IEEE Transactions on Power Electronics*, pp. 1–14, 2023.

- [40] B. McGrath and D. Holmes, "Multicarrier PWM strategies for multilevel inverters," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4, pp. 858–867, 2002.

- [41] I. Petric, "Analysis of multi-sampled pulsewidth modulation and its application in grid-tied converters," Ph.D. dissertation, Dept. Inf. Eng., Univ. Padova, Padova, Italy, 2023.

Ruzica Cvetanovic (Student Member, IEEE) was born in Belgrade, Serbia, in 1996. She received the B.S. and M.S. degrees in electrical engineering from the University of Belgrade, Belgrade, in 2019 and 2020, respectively. Since 2022, she has been working toward the Ph.D. degree with the Power Electronics Group, Department of Information Engineering, University of Padova, Padova, Italy.

From 2020 to 2021, she worked with the Power Converters and Systems Group, School of Electrical Engineering, University of Belgrade. In 2021, she

joined the Power Electronics Group, Department of Information Engineering, University of Padova, as a Visiting Researcher. Her research interests include modeling and digital control of grid-tied power electronics converters.

**Ivan Z. Petric** (Member, IEEE) was born in Belgrade, Serbia, in 1994. He received the B.Sc. and M.Sc. degrees in electrical engineering from the University of Belgrade, Serbia, in 2017 and 2018, respectively, and the Ph.D. degree in electrical engineering from the University of Padova, Italy, in 2023.

From 2018 to 2019, he was a Researcher with the Power Electronics, Machines and Control Group, The University of Nottingham, U.K. In 2022, he was a Visiting Researcher with the Electrical Engineering

and Computer Sciences Department, University of California, Berkeley, CA, USA. His research interests include modeling and control of power converters, advanced modulation strategies, and grid-connected converters for renewable energy sources and smart microgrids.

Paolo Mattavelli (Fellow, IEEE) received the MS degree (with honors) and the Ph. D. degree in electrical engineering from the University of Padova (Italy) in 1992 and in 1995, respectively. From 1995 to 2001, he was a researcher at the University of Padova. From 2001 to 2005 he was an associate professor at the University of Udine, where he led the Power Electronics Laboratory. In 2005 he joined the University of Padova in Vicenza with the same duties. From 2010 to 2012 he was with the Center for Power Electronics Systems (CPES) at Virginia

Tech. He is currently a professor at the University of Padova. His major field of interest includes analysis, modeling and analog and digital control of power converters, grid-connected converters for renewable energy systems and micro-grids, high-temperature and high-power density power electronics. In these research fields, he has been leading several industrial and government projects. His current google scholar h-index is 81. From 2003 to 2012 he served as an Associate Editor for IEEE Transactions on Power Electronics. From 2005 to 2010 he was the IPCC (Industrial Power Converter Committee) Technical Review Chair for the IEEE Transactions on Industry Applications. For terms 2003-2006, 2006-2009 and 2013-2015 he has been a member-atlarge of the IEEE Power Electronics Society's Administrative Committee. He also received in 2005, 2006, 2011 and 2012 the Prize Paper Award in the IEEE Transactions on Power Electronics and in 2007, the 2nd Prize Paper Award at the IEEE Industry Application Annual Meeting. He is an IEEE Fellow and Co-Editor in Chief for the IEEE Transactions on Power Electronics.

Simone Buso (Member, IEEE) received the M.Sc. degree in electronic engineering and the Ph.D. degree in industrial electronics from the University of Padova, Italy, in 1992 and 1997, respectively. He is currently an Associate Professor of electronics with the Department of Information Engineering (DEI) at the University of Padova. His main research interest are in the industrial and power electronics fields and are related specifically to switching converter topologies, digital control of power converters, renewable energy sources and smart micro-grids.